在低速PCB设计中,走线长短似乎无关紧要,只要连通就能正常工作,但进入MHz以上高速电路、高频射频电路后,走线长度直接决定信号质量、系统稳定性,长度不匹配引发的信号偏斜更是导致产品失效的常见元凶。

Q1:什么是PCB走线长度匹配?哪些信号必须做长度匹配?

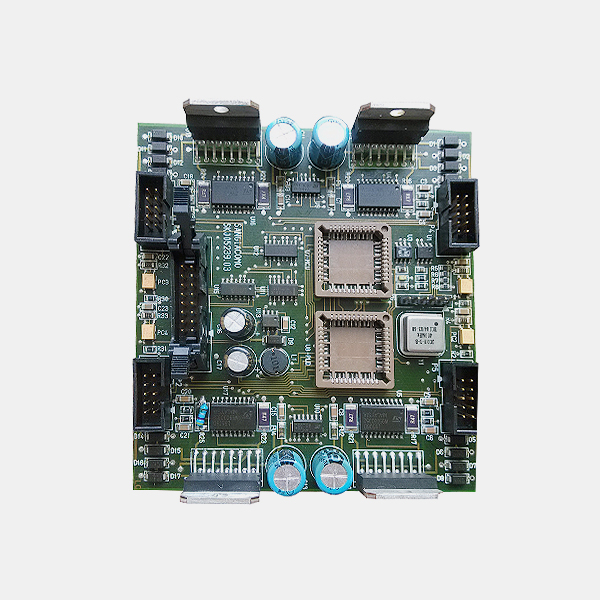

PCB走线长度匹配,简单来说就是同一组功能相关的信号链路,走线的物理长度(电气长度)严格控制在规定公差范围内,保证各路信号同步到达接收端,避免出现传输延时差异。不是所有信号都需要长度匹配,低速信号(比如普通GPIO、低频电源信号)频率低、周期长,微小的长度差异带来的延时可以忽略,无需刻意匹配;但高速差分信号、并行总线信号、多通道同步信号、时钟信号、射频收发信号,必须强制做长度匹配。

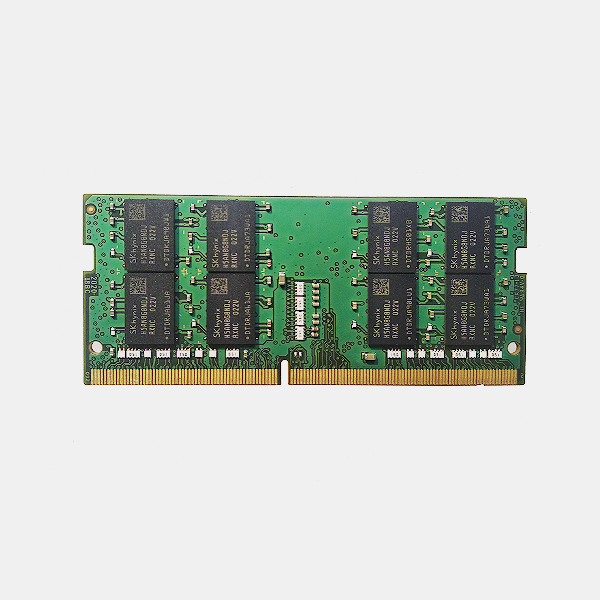

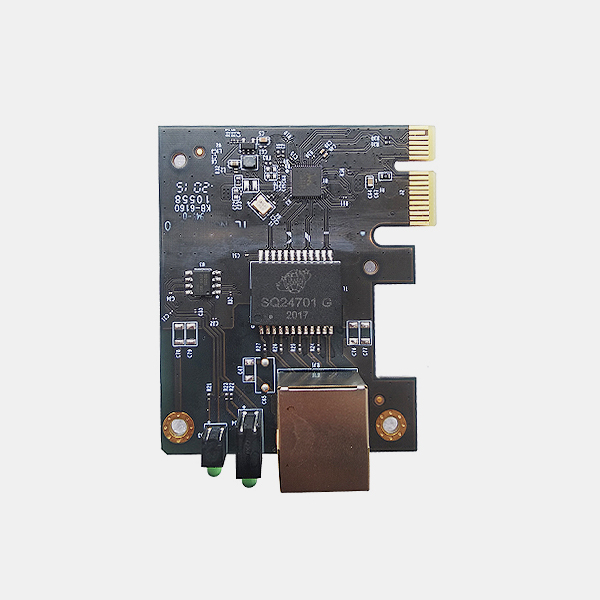

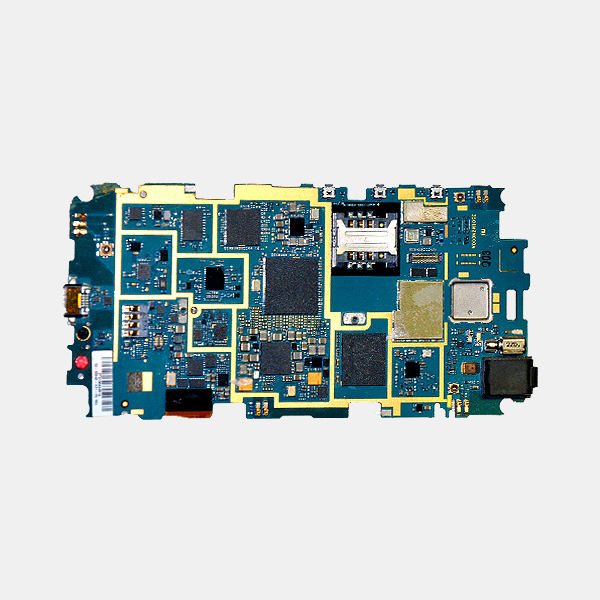

比如DDR3/DDR4/DDR5并行数据总线、USB3.0/PCIe差分对、LVDS信号、多通道ADC/DAC同步信号、雷达射频收发链路,这些信号频率高、边沿速率快,对时序精度要求极高,哪怕几毫米的长度差,都会引发明显的信号偏斜,导致采样错误、数据丢包、串扰加剧、系统误码。通俗来讲,长度匹配就是让“信号队伍”同步出发、同步到达,不出现个别信号“掉队”或“超前”的情况。

Q2:什么是信号偏斜?它和走线长度不匹配有什么直接关系?

信号偏斜(Skew),也叫时序偏斜、延时偏斜,指同一组相关信号之间,从发送端输出到接收端输入的传输时间差值,单位通常是ps(皮秒)或ns(纳秒)。信号偏斜分为两种:一种是差分对内偏斜,也就是差分信号的正负极走线长度不一,导致差分对内部两路信号不同步;另一种是组间偏斜,即并行总线内多路单端信号之间的延时差。

走线长度不匹配是引发信号偏斜的最核心、最直接的原因。信号在PCB介质中传输的速度是固定的,常规FR4板材中,信号传输速度约为6英寸/ns(15.24cm/ns),换算下来,每1mm的长度差,会带来约6.56ps的传输延时差。看似微小的延时差,在高速信号边沿时间只有几十ps的场景下,会直接导致接收端采样窗口错位,比如时钟信号和数据信号不同步,接收芯片无法正确抓取数据电平,进而出现逻辑错误、系统死机,高频场景下还会引发信号反射、谐振,恶化EMC性能。

Q3:长度匹配只看物理长度吗?电气长度和物理长度有什么区别?

很多新手设计师会陷入一个误区:只盯着走线的物理长度做匹配,忽略了电气长度,最终导致匹配失效。物理长度是走线的实际物理尺寸,而电气长度是信号实际传输的有效长度,才是决定信号延时的关键。

电气长度受三个因素影响:一是PCB介质的介电常数(Dk),介电常数越大,信号传输速度越慢,相同物理长度下电气长度越长;二是走线的阻抗与传输线类型,微带线和带状线的信号传输速度不同,同一物理长度的带状线,延时会比微带线略大;三是过孔、焊盘、拐角、串扰带来的附加延时,每一个过孔相当于增加了1-3mm的物理走线延时,直角拐角、粗糙铜箔也会小幅增加信号延时。因此,做长度匹配时,不能只算直线物理长度,必须把过孔、拐角、介质差异带来的等效长度都计入,实现电气长度匹配,这才是真正有效的长度匹配。

Q4:信号偏斜的容忍度是多少?长度匹配公差怎么定?

信号偏斜的容忍度没有固定值,核心由信号频率、边沿速率、接收端采样窗口决定。通用设计准则是:组间信号偏斜不能超过信号边沿时间的1/5,差分对内偏斜不能超过信号边沿时间的1/10,同时不能超过时钟周期的1/20。

举个实际例子,DDR5数据信号边沿时间约50ps,那么组间偏斜要控制在10ps以内,对应物理长度差不超过1.5mm;PCIe 4.0差分信号对内偏斜要控制在5ps以内,物理长度差几乎要控制在0.5mm以内。低速高速信号(如100MHz以内并行总线),偏斜容忍度可放宽至50-100ps,长度差控制在5-10mm即可。实际设计中,优先查看芯片 datasheet 中的时序要求,按照芯片手册给出的最大偏斜值,反推走线长度匹配公差,这是最严谨的做法。

PCB走线长度匹配是高速PCB设计的基础门槛,核心目标是消除信号偏斜、保证时序同步,区分低速和高速信号的匹配需求、分清物理长度和电气长度的差异,是避免基础设计错误的关键。只有理解了底层逻辑,后续的布局布线、偏斜优化才能精准落地,不会做无用功。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)