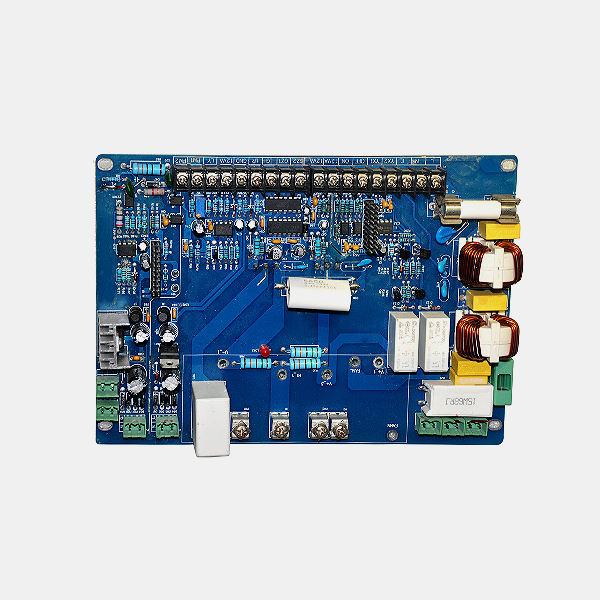

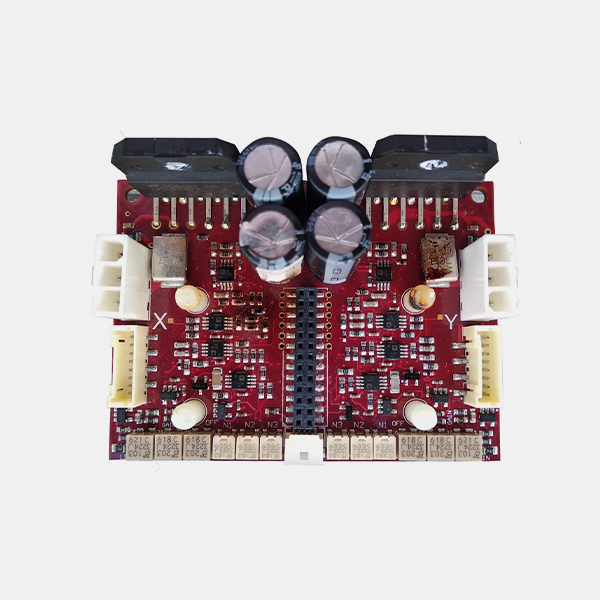

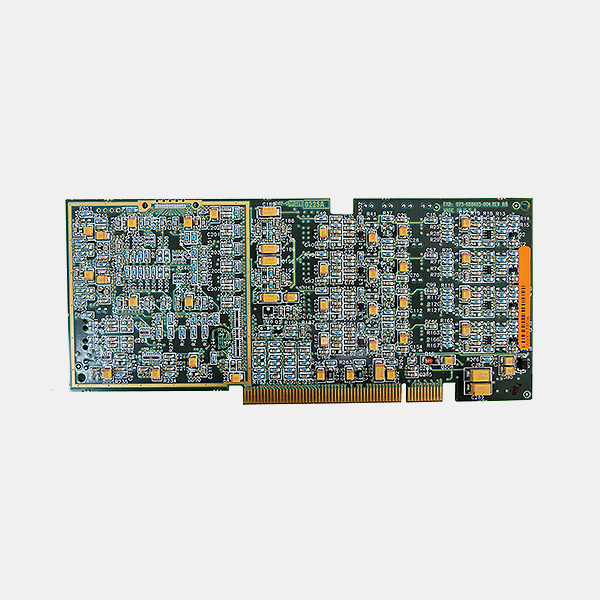

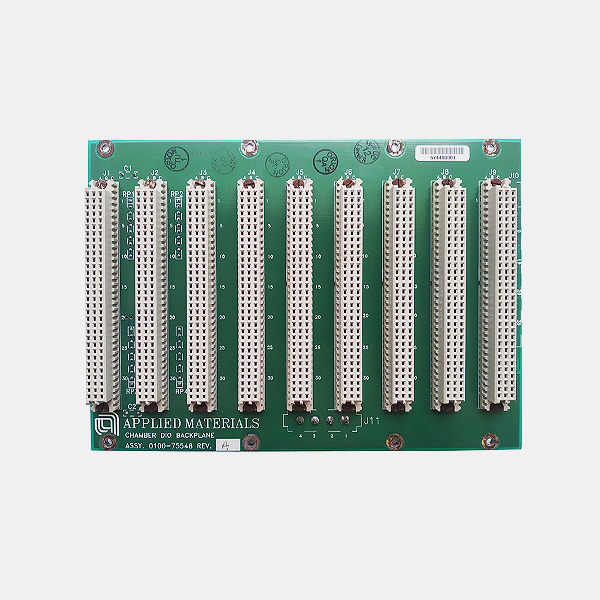

在拥挤的PCB电路板上,密密麻麻的走线像极了高峰期挤在一起的人群,人与人之间会互相推搡、干扰,而PCB走线上的电信号之间,也存在这样的“无形推搡”,那就是串扰。业内常把串扰戏称为“信号小偷”,它不破坏元器件,不烧断走线,却会悄悄偷走一部分信号能量,从一条走线转移到相邻走线,让原本干净的信号混入杂波,导致电路功能紊乱。

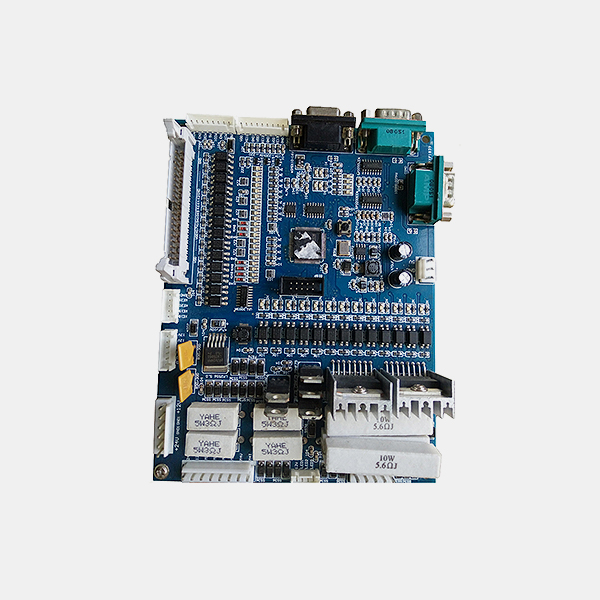

先明确串扰的专业定义:PCB串扰是指两条或多条相邻的PCB走线之间,由于存在寄生电容和寄生电感,一条走线上的传输信号(干扰线),通过电磁场耦合的方式,将部分信号能量感应到相邻走线(被干扰线)上,产生无用的干扰信号,进而影响被干扰走线正常信号传输的现象。简单来说,就是两条靠得太近的走线,互相“偷听”了对方的信号,干扰线把自己的信号内容泄露给了被干扰线,导致被干扰线收到错误信号。根据干扰信号的传输方向,串扰分为近端串扰和远端串扰,近端串扰发生在干扰线的信号发送端同侧,远端串扰发生在干扰线的信号接收端同侧,高速电路中远端串扰的危害更明显,也是排查的重点。

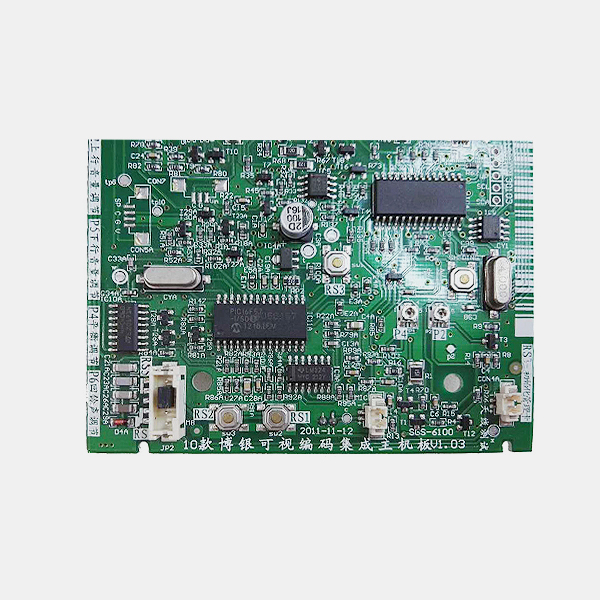

串扰的危害极具隐蔽性,属于典型的“小病拖成大病”,初期轻微串扰很难被发现,只会让信号信噪比略有下降,一旦积累到一定程度,就会引发各类莫名其妙的故障。最直观的危害是信号失真、数据误码,被干扰走线上的有用信号混入串扰噪声后,波形变得杂乱,高低电平阈值模糊,数字电路中会出现数据传输错误、逻辑判断失误,比如单片机的IO口误触发、串口通信丢包、显示屏花屏、传感器数据跳动;模拟电路中,串扰会导致音频电路出现杂音、射频电路信号衰减、电源纹波增大,影响电路的精度和稳定性。在高密度PCB中,大量走线互相串扰,还会引发系统性的电磁干扰问题,导致设备无法通过EMC认证,甚至干扰周边其他电子设备的正常工作。更棘手的是,串扰故障很难精准定位,因为它和走线间距、长度、层叠、参考平面都有关系,新手工程师往往排查很久都找不到根源,浪费大量时间和精力。

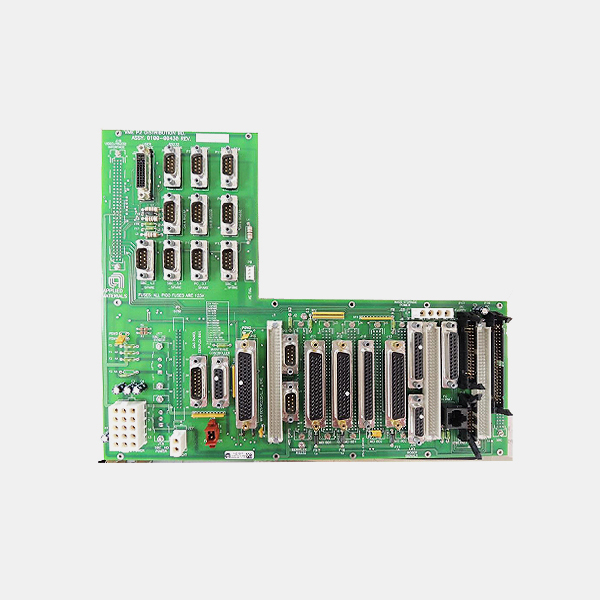

串扰的本质是电磁场耦合,核心成因分为电容性耦合和电感性耦合,两者同时存在,共同加剧串扰程度。电容性耦合源于两条走线之间的寄生电容,干扰线上的电压变化,会通过寄生电容对被干扰线充电,形成电压型干扰,走线间距越小、平行长度越长,寄生电容越大,串扰越严重;电感性耦合源于两条走线之间的寄生电感,干扰线上的电流变化产生交变磁场,磁场穿过被干扰线感应出感应电压,形成电流型干扰,高速信号的边沿变化速率越快,磁场变化越剧烈,电感性串扰越明显。除此之外,PCB设计中的多个不合理设计,都会放大串扰:一是高速信号走线与敏感信号走线平行布线,且间距过小,没有预留足够的安全距离;二是PCB层叠设计不合理,没有完整的地平面隔离,不同层的走线垂直交叉不足,平行重叠过多;三是走线过长,没有合理分区,电源走线和信号走线混布;四是过孔密集、布线杂乱,破坏了电磁场的稳定分布;五是阻抗不匹配引发的信号反射,进一步叠加串扰噪声,形成恶性循环。

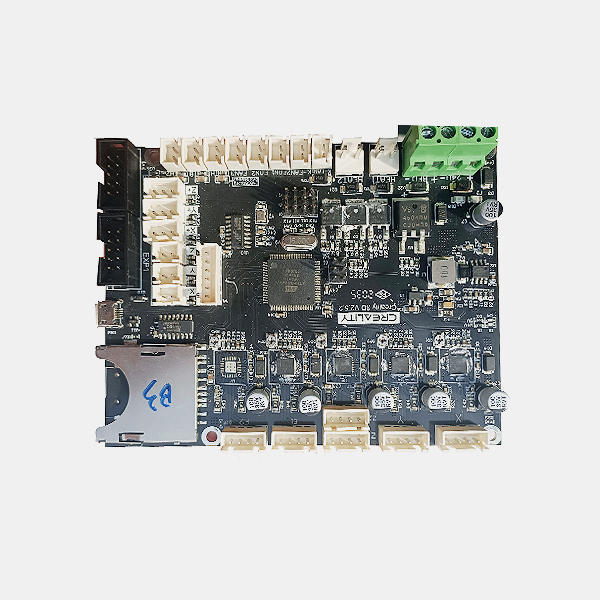

想要防范PCB串扰,核心思路是拉大走线间距、切断耦合路径、优化电磁场分布,具体实操方法简单易上手,适合各类PCB设计场景。首先是把控走线间距,遵循“3W原则”,即两条走线的中心间距大于等于3倍走线宽度,高速敏感信号间距可以扩大到5W,从物理距离上减少寄生电容和电感;其次是优化布线走向,高速信号、时钟信号、射频信号等干扰源走线,严禁与模拟信号、弱信号、传感器信号等敏感走线平行布线,尽量采用垂直交叉布线,避免长距离平行;然后是分层隔离,设置完整的地平面和电源平面,高速走线和敏感走线分不同层布置,中间用地平面隔离,阻断电磁场耦合;第四是短化走线长度,尤其是高速时钟线和敏感信号线,尽量缩短走线,减少平行耦合的距离;第五是添加防护措施,在关键敏感走线两侧添加接地保护线,形成屏蔽效果,吸收耦合干扰,同时避免走线出现尖角、分叉,减少电磁场辐射;最后是合理布局,把干扰性强的元器件和敏感元器件分开布局,从源头减少走线交叉干扰。

很多工程师觉得串扰是高密度高速板才要考虑的问题,其实不然,哪怕是普通的低频小信号板,不合理的布线也会引发串扰,导致电路工作不稳定。串扰的防控没有绝对的零串扰,只有把串扰控制在允许范围内,不影响电路正常功能即可。在PCB设计中,提前做好布线规划,遵守基本的抗串扰规范,远比后期排查故障更高效。只要吃透串扰的耦合原理,掌握基础的防控技巧,就能轻松守住信号完整性,让电路板上的每条走线都能“各司其职”,杜绝互相干扰的乱象。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)