你有没有遇到过这样的情况:明明原理图设计得完美无缺,仿真波形也很漂亮,可一打板调试,信号就出问题了?高速信号线上出现严重的过冲、振铃,甚至整个系统都因此不稳定?这时候你可能会怀疑是不是芯片有问题,或者焊接工艺有瑕疵。但实际上,问题的根源很可能藏在PCB设计中那些被忽略的"高速"细节里。

很多工程师从低速设计转向高速设计时,都会经历这个阵痛期。低速电路中,我们习惯用"导线就是导线"的思维方式,认为只要连通就行。但当信号频率提升到一定程度,事情就没那么简单了——PCB走线不再是简单的连接线,而是复杂的传输线;信号不再是理想的变化,而是包含反射、串扰、损耗的复杂波形。

今天我们就来系统梳理PCB高速信号设计的核心理论基础。不讲玄虚,只讲干货,帮你建立正确的高速设计思维框架。

一、什么是"高速信号"?——频率不是唯一标准

很多新手工程师会问:"我的时钟信号只有50MHz,算高速吗?"这是个典型的问题。遗憾的是,答案不是简单的"是"或"否"。

判断信号是否为高速,关键不在于频率本身,而在于信号的上升沿时间。

当信号的上升沿时间(tr)小于信号在PCB上传输时间的1/4时,就必须按照高速信号来对待。这个临界点对应的物理意义是:信号在PCB走线上的传输延迟已经足够长,使得信号还没来得及完全到达接收端时,源端已经开始变化了。

用公式表达就是:

tr ≤ 2 × tpd

其中tr是上升沿时间,tpd是信号在传输线上的单向传输延迟。

举个例子:假设你使用FR4材料(介电常数约4.2),PCB走线长度为15cm,信号传输速度约为14cm/ns(光速的一半),那么单向传输延迟约为1.07ns。如果你的信号上升沿时间小于2.14ns,就必须按高速信号设计。

这就是为什么100kHz的方波也可能是高速信号——因为它的上升沿可能只有几纳秒甚至几百皮秒。反之,一个1GHz的正弦波如果上升沿很缓,反而可能不需要太严格的高速设计处理。

记住这个结论:频率决定带宽,但上升沿决定是否高速。

二、传输线理论基础——PCB走线的真实面目

在低速设计中,我们把PCB走线看作理想导线,认为信号瞬间从一端传到另一端。但在高速条件下,这个假设完全失效。PCB走线必须被建模为传输线。

传输线是什么?

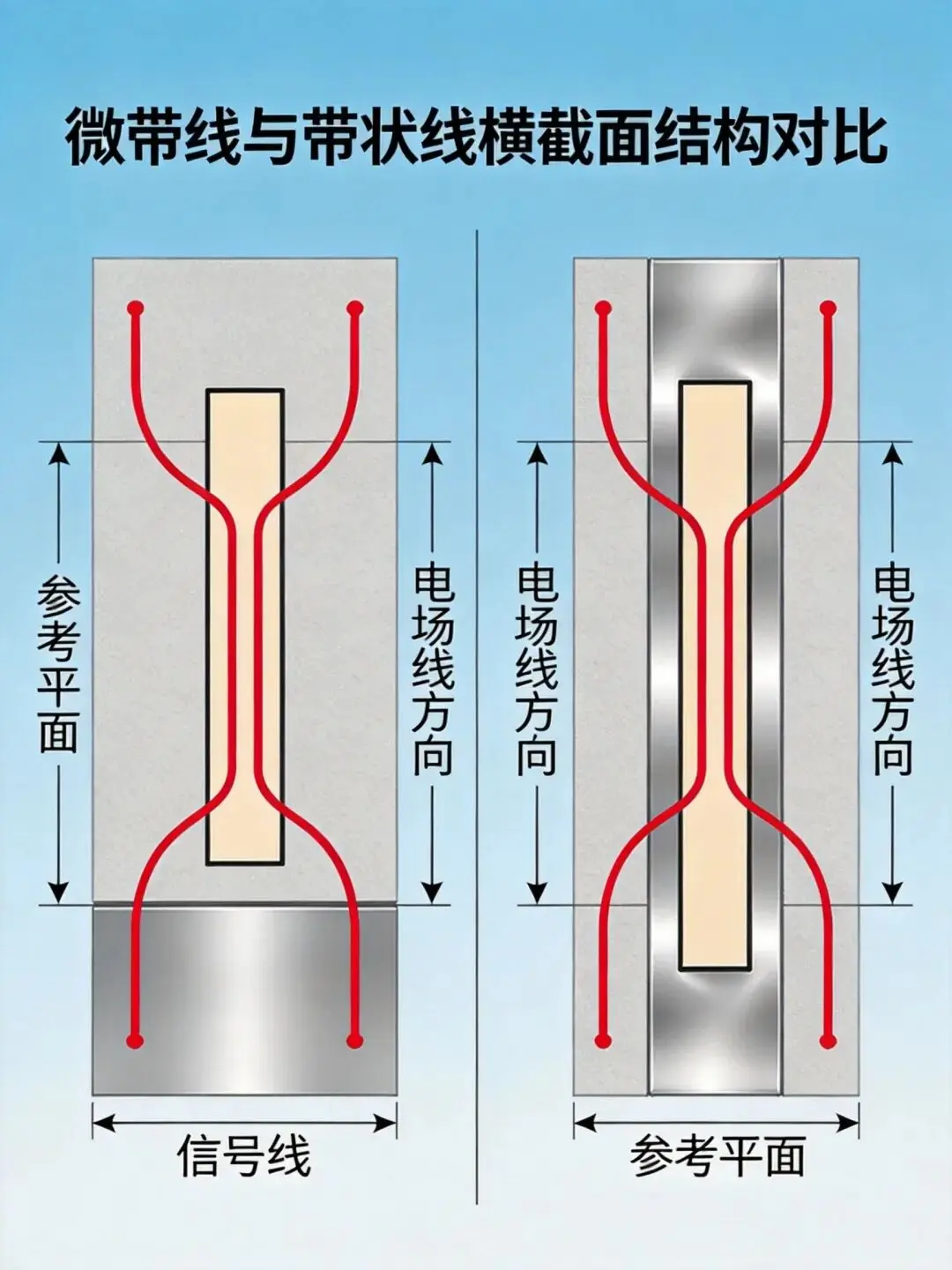

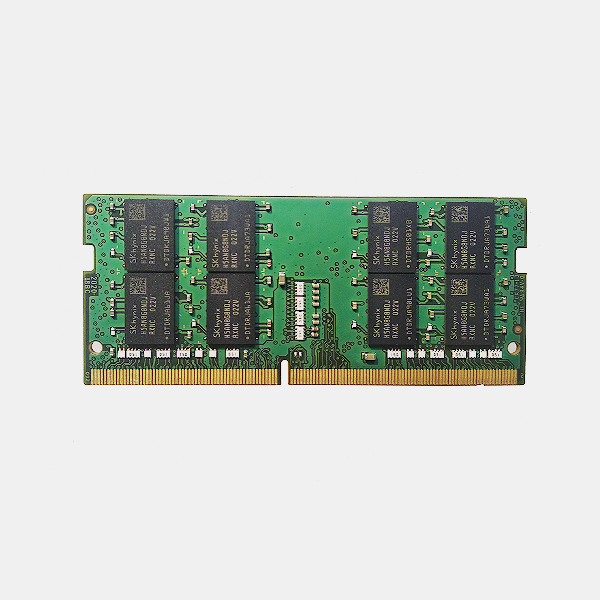

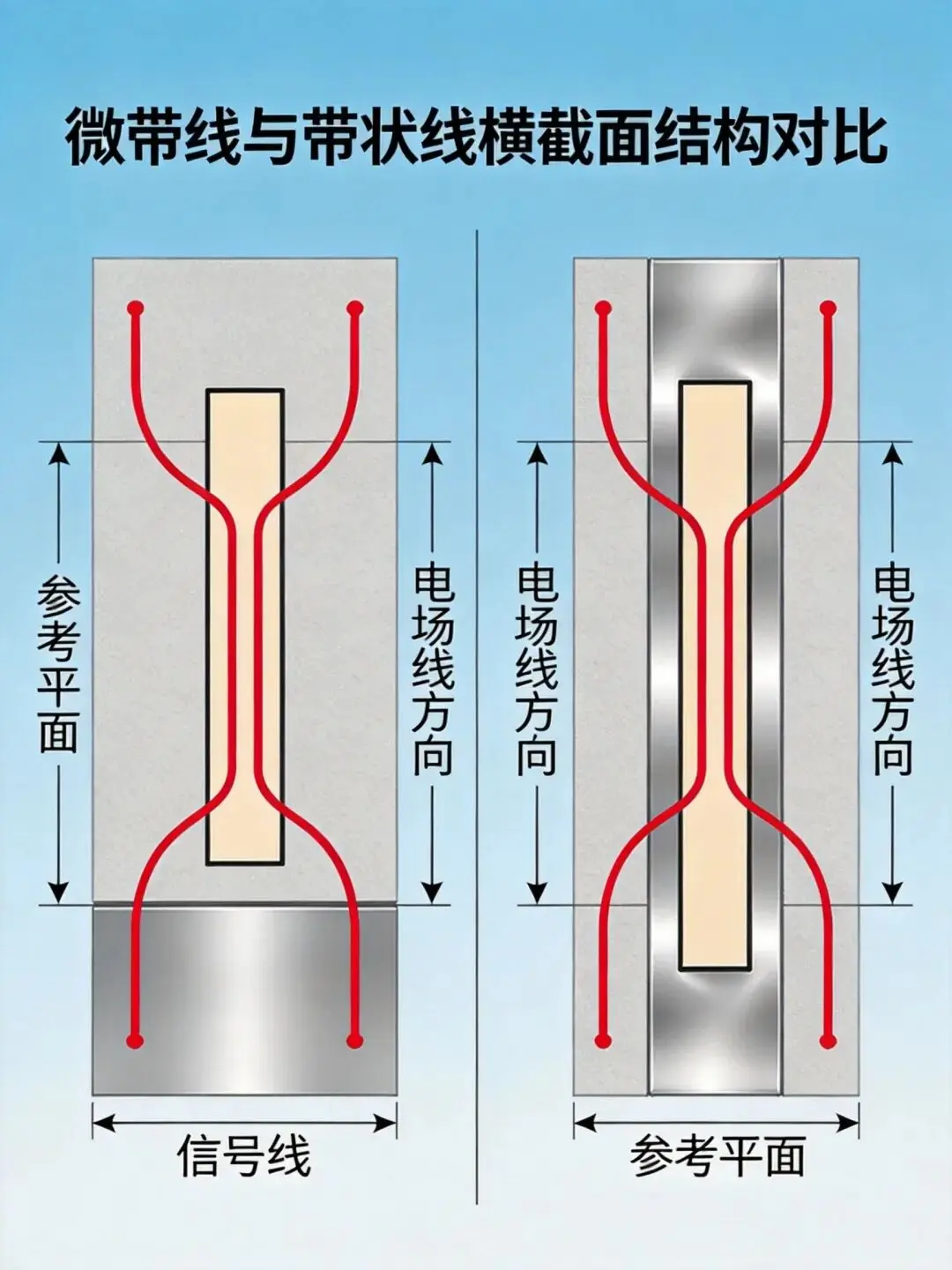

从物理学角度看,传输线是由分布参数(电阻、电感、电容、电导)组成的系统。在PCB上,微带线和带状线是最常见的传输线形式。

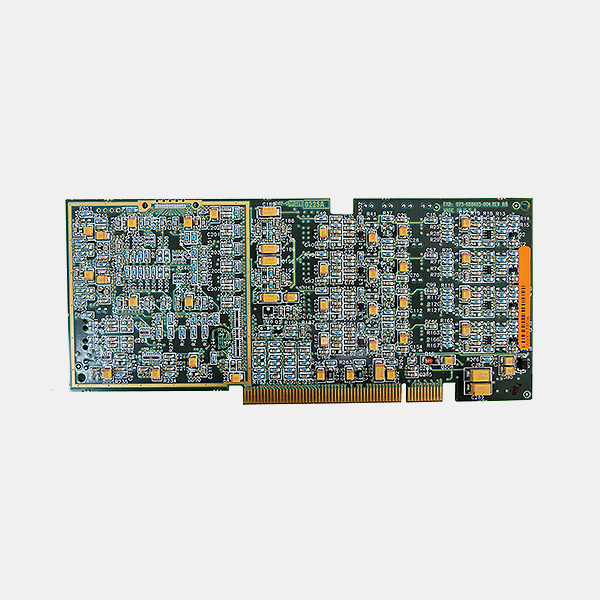

图注:上图展示了微带线(左)和带状线(右)的横截面结构。可以看到,微带线的信号线在表层,电场部分在空气中;带状线的信号线夹在两层参考平面之间,电场完全封闭在介质中。两种结构的特性阻抗、传播速度和抗干扰能力都有显著差异。

理解传输线,关键要掌握四个核心参数:

特性阻抗(Z0)

:传输线的固有属性,取决于线宽、介质厚度、介电常数等几何参数。典型值有50Ω、75Ω、100Ω等。

传播速度

:信号在传输线上传播的速度。FR4材料中约为14cm/ns,约为光速的一半。

传播延迟

:信号通过单位长度传输线所需的时间。FR4材料中约为70ps/cm。

衰减

:信号在传播过程中能量逐渐损失的现象,包括导体损耗、介质损耗和辐射损耗。

特性阻抗的重要性

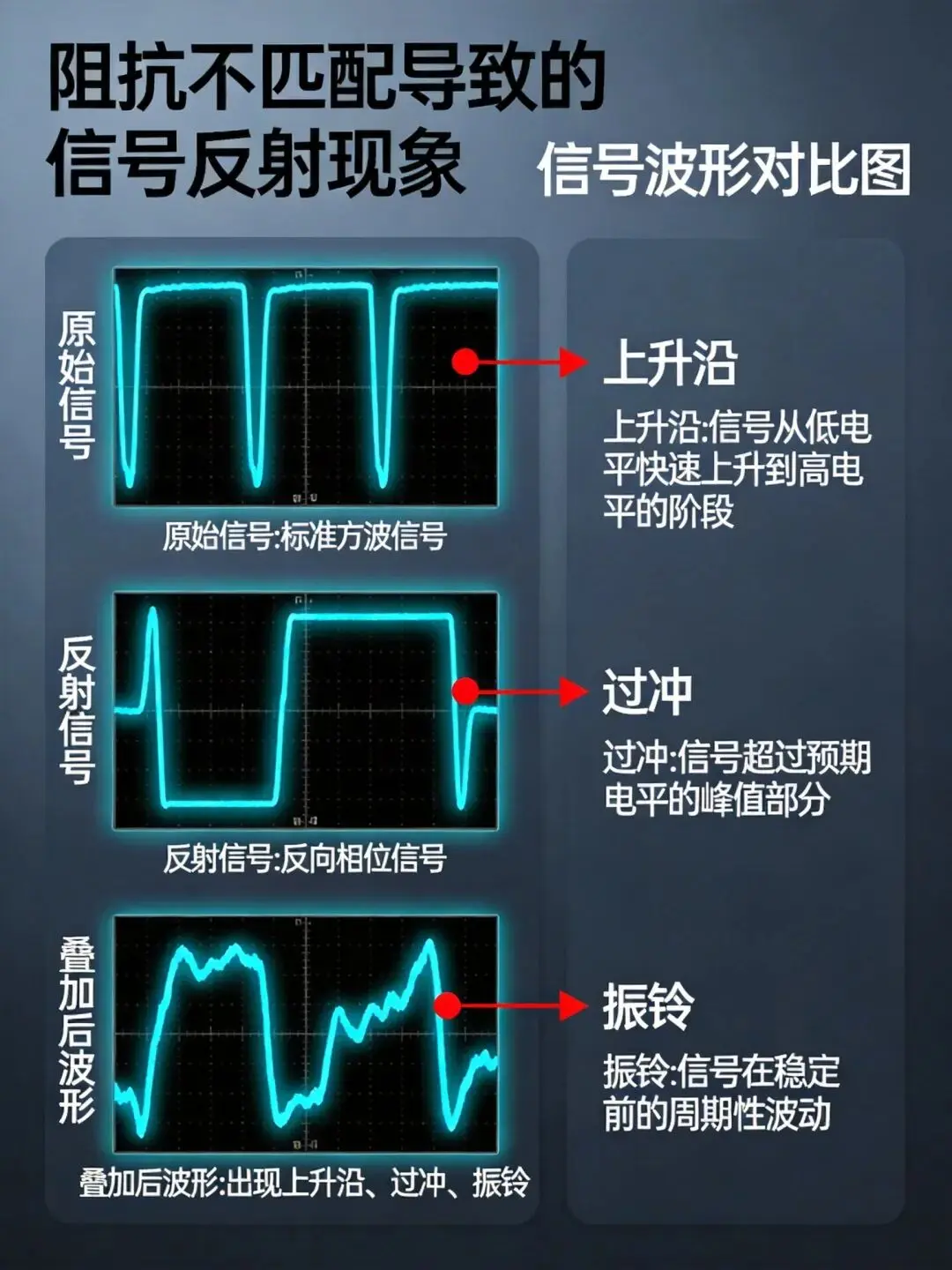

特性阻抗是高速设计中最重要的概念之一。如果源端阻抗、传输线阻抗和负载阻抗不匹配,就会发生信号反射。

想象一下,你往水管里突然注水,水管末端如果是封闭的,水波会反射回来;如果末端是开放的,水波也会以不同方式反射。电信号在传输线上的行为完全类似——阻抗不匹配点就是"水管的不连续处",信号会在这些地方发生反射。

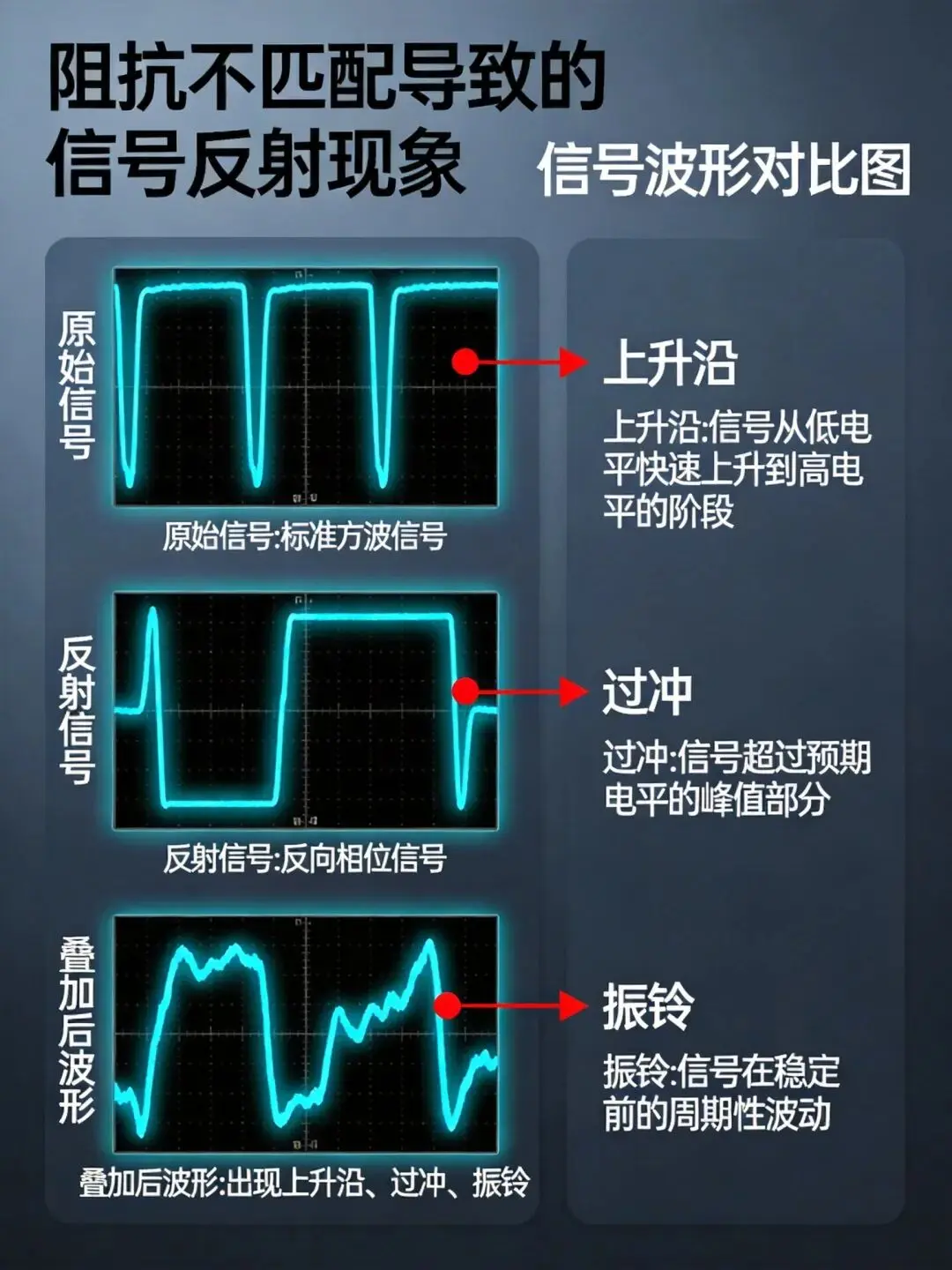

反射会造成什么后果?过冲、振铃、甚至逻辑错误。这就是为什么在高速设计中,"阻抗匹配"是必须遵守的基本原则。

图注:上图展示了阻抗不匹配导致的信号反射现象。原始理想方波(绿色)经过传输线后,由于反射叠加,在接收端产生了明显的过冲(红色箭头)和振铃(蓝色箭头)。这些畸变可能导致信号误判或芯片损坏,必须通过阻抗匹配来消除。

三、信号反射与端接技术——阻抗匹配的实战应用

既然阻抗不匹配会导致反射,那如何解决?答案是端接技术。

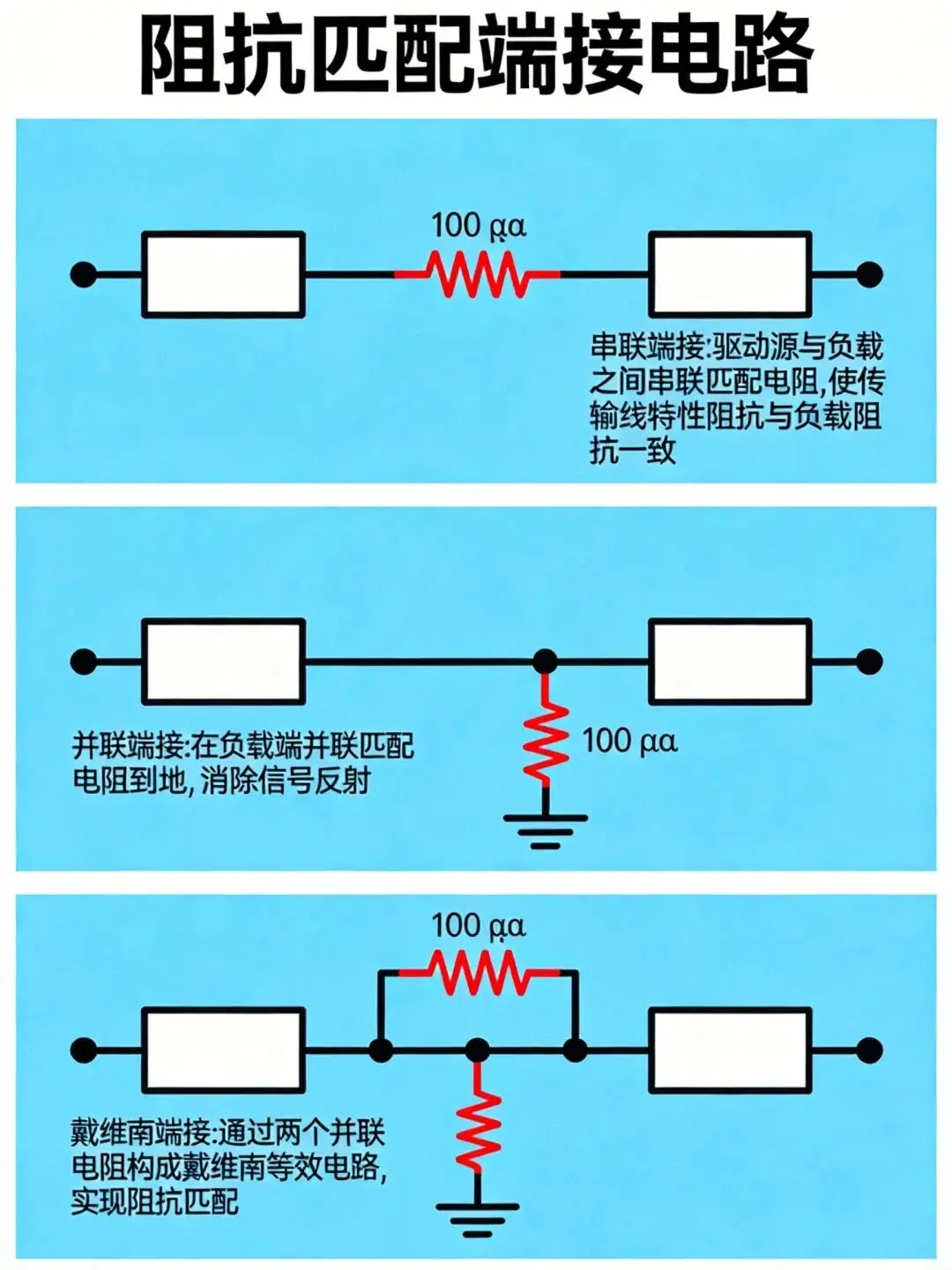

端接的本质是让信号"看到"的阻抗始终一致,从而消除反射。常见的端接方式有以下几种:

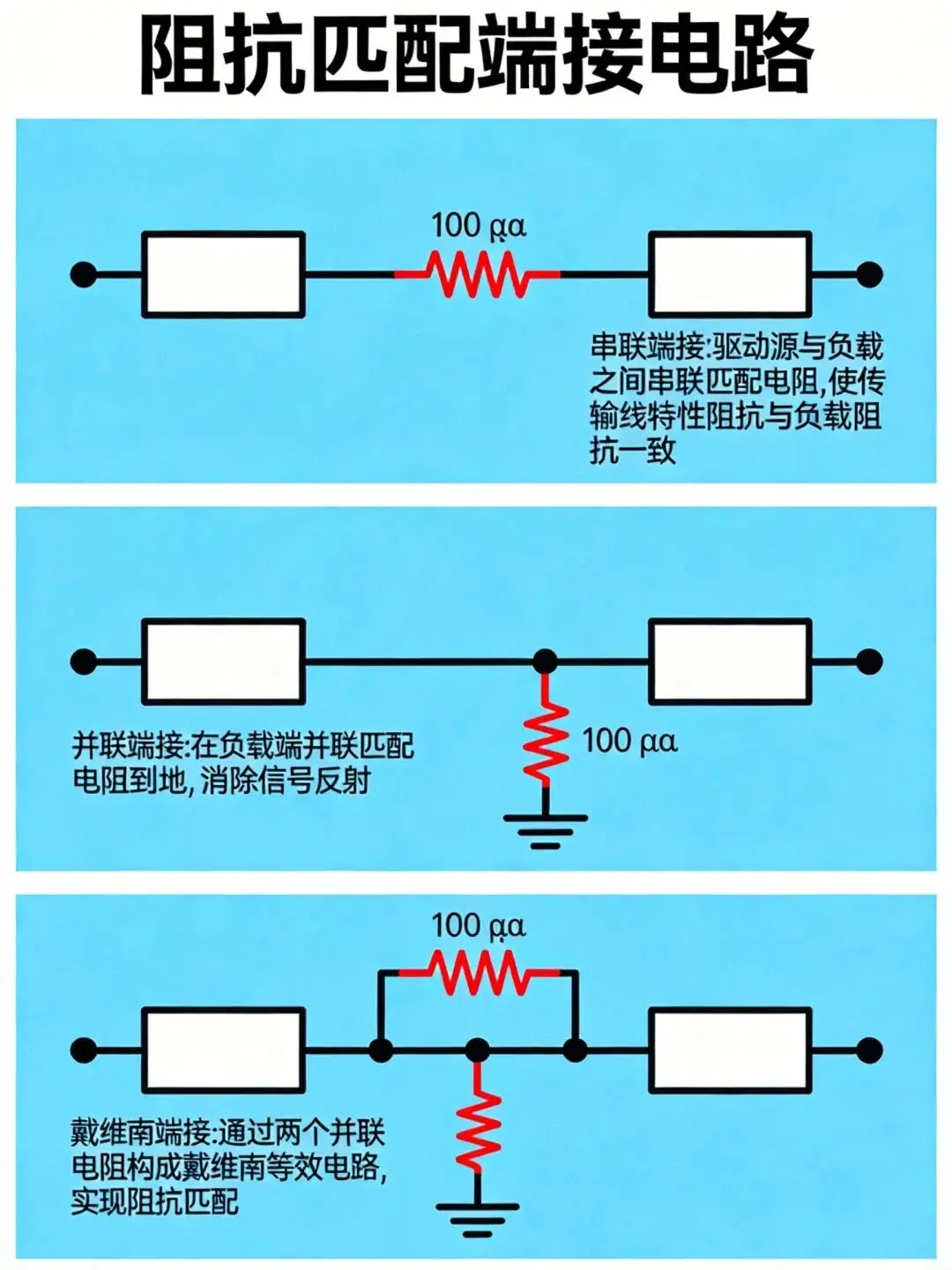

1. 并行端接

在负载端并联一个电阻到地或电源,使得负载阻抗等于传输线阻抗。

优点:实现简单,效果稳定。

缺点:增加直流功耗,可能需要额外的电源或地平面。

典型场景:单端信号,功耗敏感度不高的应用。

2. 戴维南端接

在负载端使用两个电阻分别接到电源和地,通过分压形成匹配阻抗。

优点:提供直流偏置,适合某些需要特定共模电压的接口。

缺点:需要精确的电阻值计算,功耗较大。

典型场景:差分信号、需要直流偏置的总线。

3. 串联端接

在源端串联一个小电阻(通常为22-33Ω),使源端阻抗加上电阻值等于传输线阻抗。

优点:功耗低,实现简单。

缺点:只在负载端完全匹配时有效,长距离传输效果较差。

典型场景:点到点连接,驱动能力较强的信号。

4. 差分端接

在差分信号的接收端跨接一个电阻,匹配差分阻抗。

优点:抗干扰能力强,适合高速长距离传输。

缺点:需要成对的差分走线。

典型场景:USB、PCIe、SATA、以太网等高速差分接口。

端接电阻如何计算?

基本原则是:端接后的等效阻抗 = 传输线特性阻抗

例如,传输线阻抗为50Ω,源端驱动阻抗为10Ω,使用串联端接时,串联电阻应为40Ω(10Ω + 40Ω = 50Ω)。

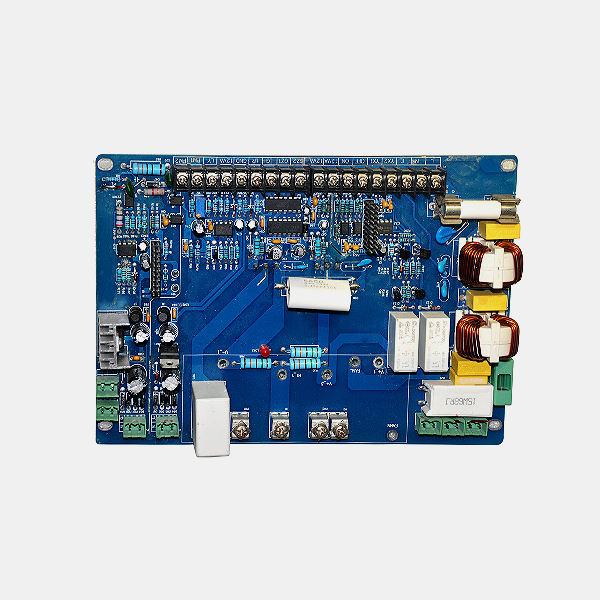

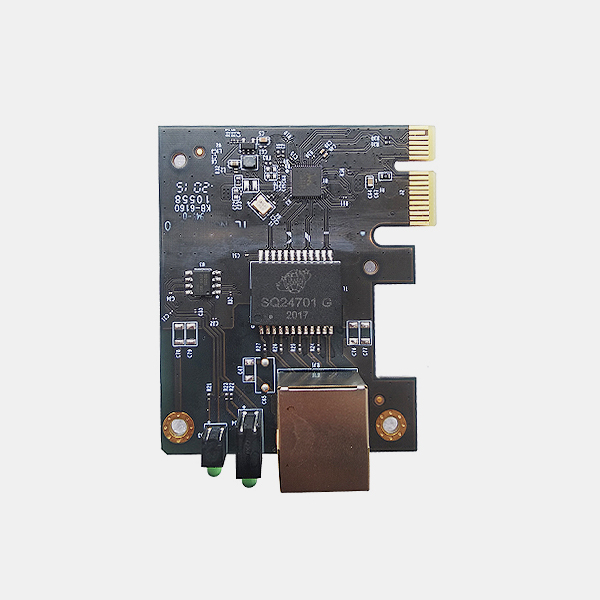

图注:上图展示了三种常用的端接电路。左图是并联端接,在负载端将电阻接至地或电源,使负载阻抗与传输线匹配;中图是戴维南端接,使用两个电阻分压提供匹配阻抗和直流偏置;右图是串联端接,在源端串联小电阻使总阻抗匹配传输线。选择端接方式时需要综合考虑功耗、驱动能力和布线空间。

四、串扰与电磁兼容——高速信号的"邻里关系"

单个信号设计好了还不够,多个信号走在一起时,还会互相影响。这种现象叫串扰。

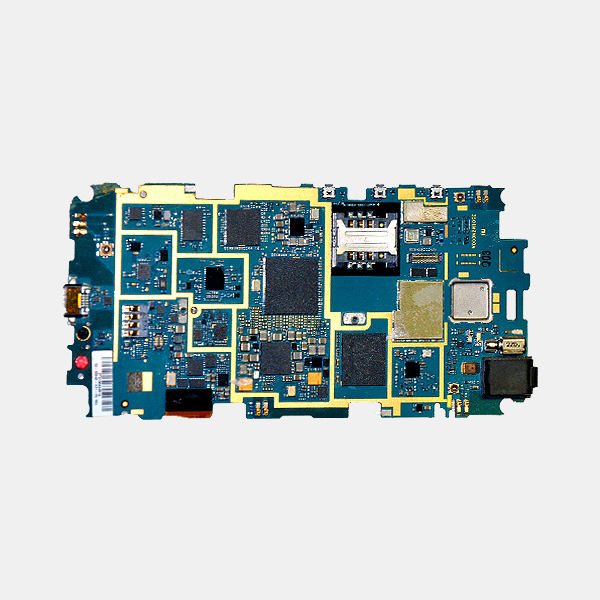

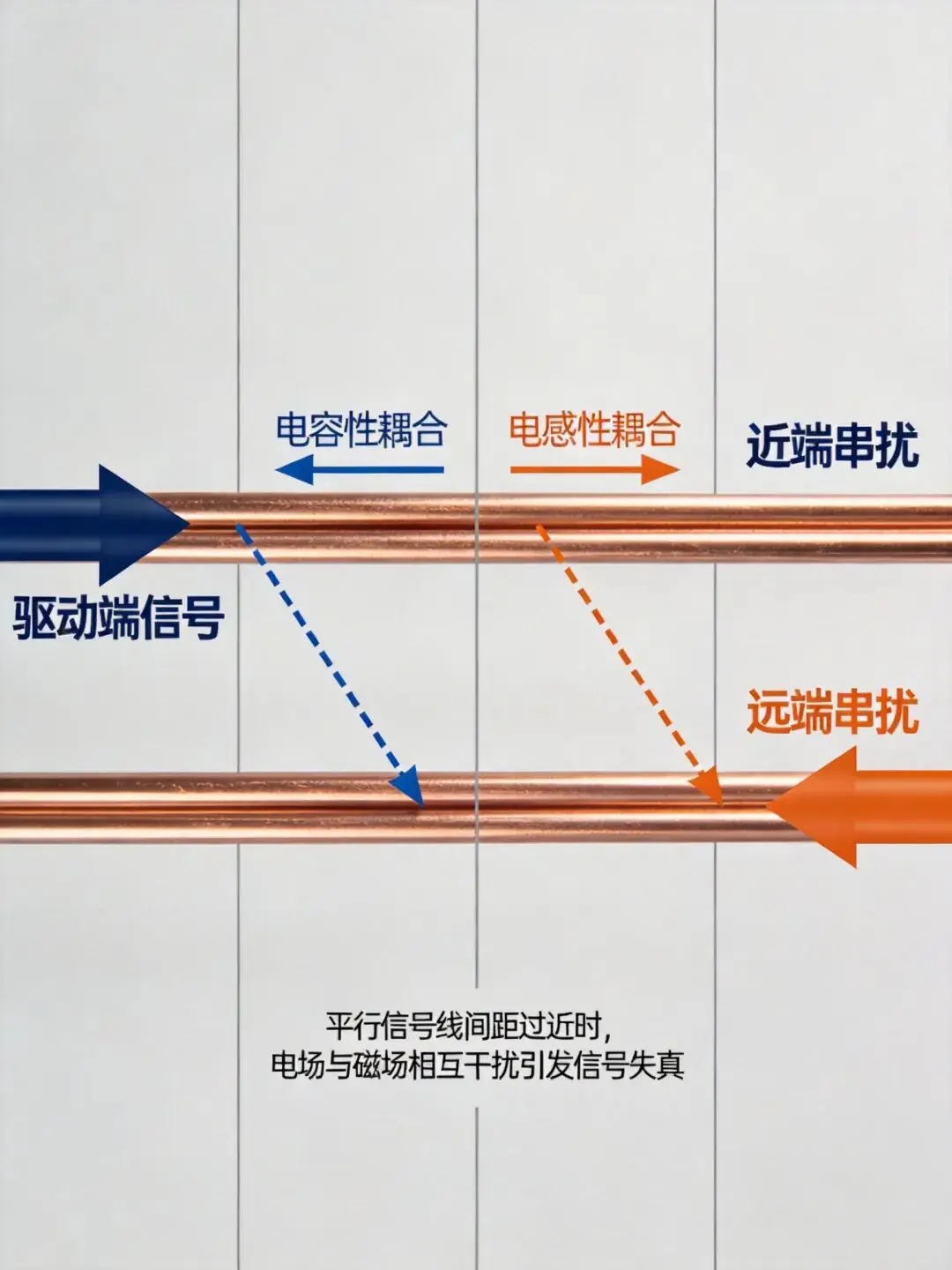

串扰的物理机制

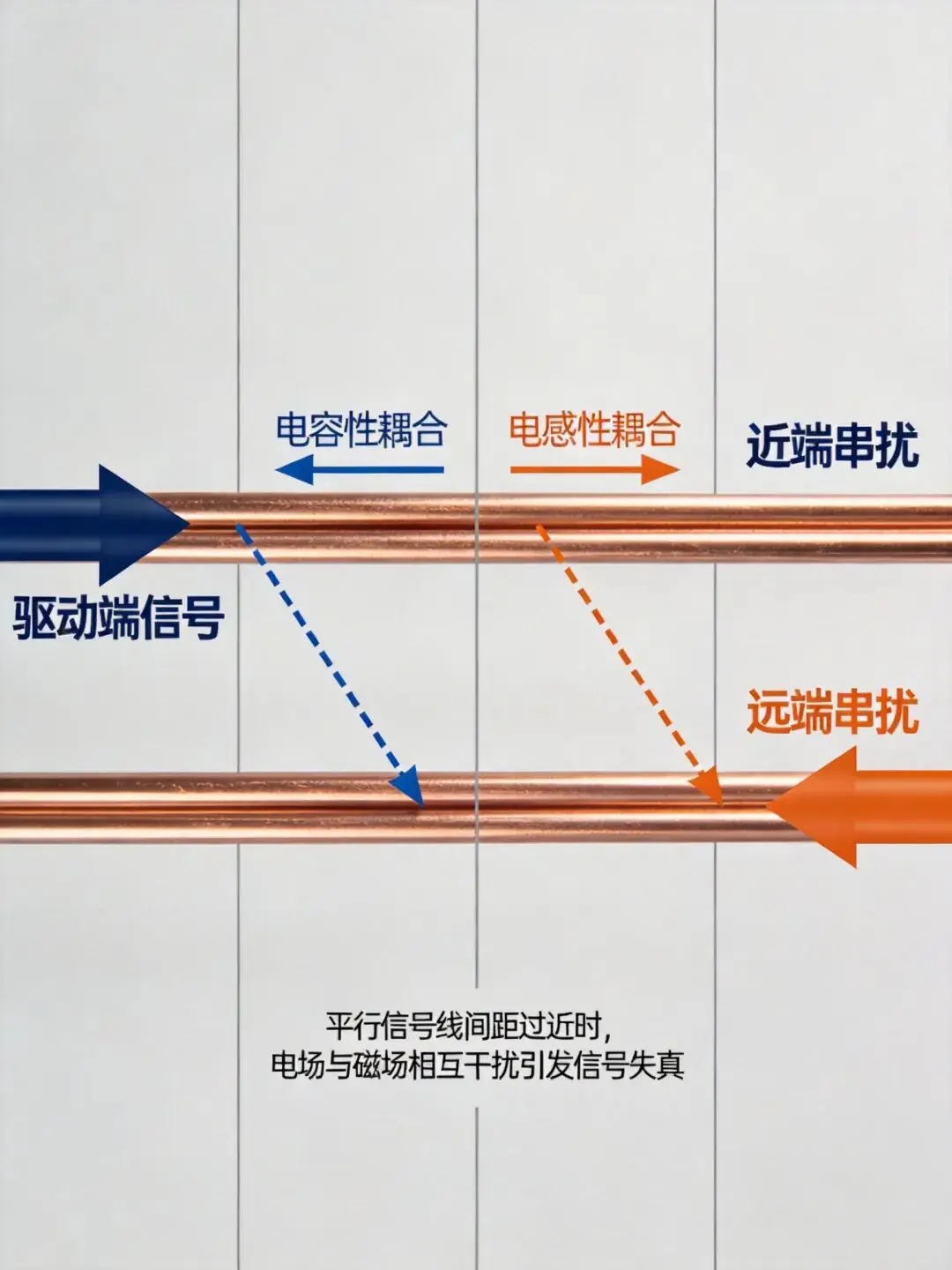

当两条PCB走线靠得很近时,它们之间存在寄生电容和寄生电感。一条信号线上的快速变化会通过这些寄生元件耦合到另一条线上,形成干扰。

串扰分为两种类型:

电容性串扰

:通过电场耦合,也叫近端串扰。受害线上会出现与攻击信号极性相同的干扰脉冲。

电感性串扰

:通过磁场耦合,也叫远端串扰。受害线上会出现与攻击信号极性相反的干扰脉冲。

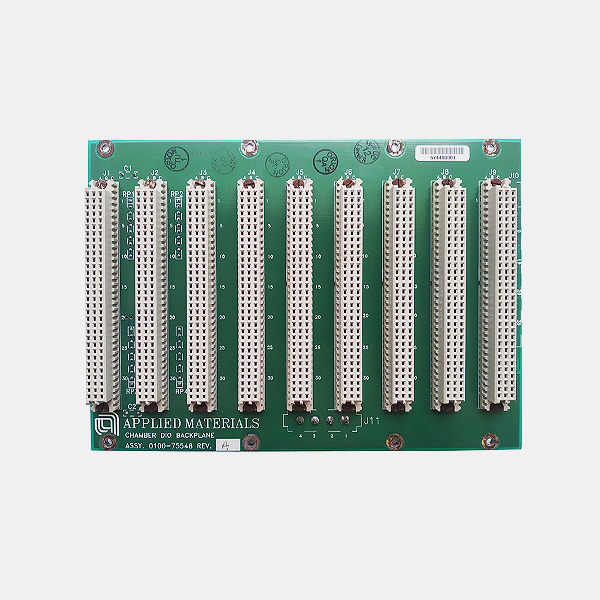

图注:上图直观展示了串扰的物理机制。当攻击信号线(绿色)上出现快速变化的信号时,电场通过寄生电容耦合到受害信号线(蓝色),形成电容性串扰;同时,变化的电流产生磁场,通过互感耦合形成电感性串扰。两种串扰在受害线上叠加,可能导致信号误判。近端串扰和远端串扰的极性和幅度不同,需要分别处理。

如何减小串扰?

增加线间距

:最直接有效的方法。一般要求线间距至少是线宽的3倍以上。

缩短平行长度

:尽量减少信号线的平行布线长度,特别是对于同步时钟和高速数据线。

使用地线隔离

:在敏感信号线之间插入地线,形成电磁屏蔽。

采用差分信号

:差分信号对外部干扰的免疫力更强,适合高速长距离传输。

层叠设计优化

:将敏感信号布置在相邻的信号层时,保证参考平面的连续性。

实战经验分享

在某个项目中,我们遇到过DDR4数据线的串扰问题。当时按照常规3W规则设计线间距,但测试时发现某些位在高速读写时出现误码。后来分析发现,同一层内有多组DDR信号线长距离平行,叠加效应导致串扰超限。解决方案是调整层叠,将不同组的信号布置在不同层,并在层间增加完整的地平面,问题得以解决。

这个案例提醒我们:设计规范是基础,但具体问题要具体分析。仿真验证和实测调试同样重要。

五、高速PCB设计的实用原则——从理论到实践

掌握了理论基础后,如何在设计中落地?以下是几个关键的设计原则:

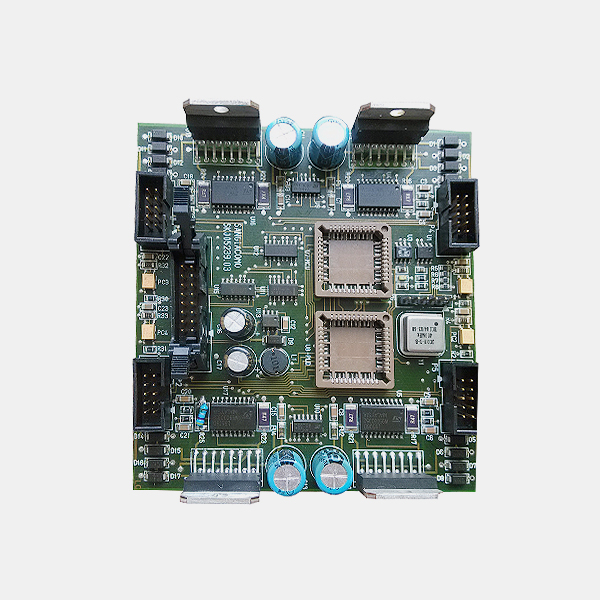

原则1:层叠设计要合理

好的层叠设计是高速PCB的基础。基本原则包括:

典型的8层板层叠设计(从顶层到底层):

顶层 - 信号(微带线) GND - 参考平面 信号 - 带状线 信号 - 带状线 PWR - 参考平面 信号 - 带状线 信号 - 带状线 底层 - 信号(微带线)

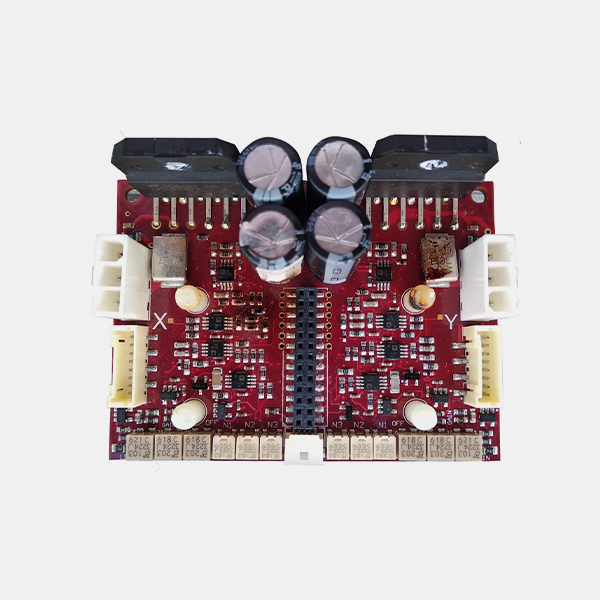

图注:上图是一个典型的8层PCB层叠结构。顶层和底层布置微带线,便于布线和调试;内层布置带状线,提供更好的信号完整性。GND和PWR平面相邻,形成良好的平板电容,为高速芯片提供稳定的电源。注意观察,信号层都与参考平面相邻,确保了阻抗的连续性和可控性。

原则2:走线规则要严格

3W原则

:线间距至少为线宽的3倍,以减小串扰。

等长匹配

:同一组差分信号或总线信号要保证等长,误差通常控制在±5mil以内。

避免直角走线

:使用45度或圆弧走线,避免90度拐角造成阻抗突变。

过孔数量要少

:过孔会造成阻抗不连续和额外的寄生电感,高速信号过孔数量要尽量少。

原则3:电源分配要稳定

高速芯片对电源质量要求极高,电源分配网络(PDN)设计必须确保:

原则4:接地策略要统一

六、仿真与调试——理论与实践的桥梁

高速PCB设计不是一次就能完美的,仿真和调试是不可或缺的环节。

为什么要仿真?

常用仿真工具

调试技巧

测量点选择

:在关键信号的源端和接收端预留测试点。

示波器带宽

:示波器带宽至少是信号最高频率分量的3-5倍。

探头影响

:高速测量时,探头会成为负载,改变信号特性。使用低电容探头或差分探头。

时序测量

:对于时钟和数据同步的接口,要测量建立时间和保持时间。

七、总结与行动建议

高速PCB设计是一个系统工程,需要理论基础、实践经验、仿真验证和调试能力的综合运用。本文梳理了从什么是高速信号,到传输线理论、阻抗匹配、串扰抑制等核心概念,希望能帮你建立完整的知识框架。

看完这篇文章,你可以做这些事情:

回顾你的项目

:找出你曾经遇到过的信号完整性问题,用文中的理论重新分析,看是否有更优的解决方案。

动手仿真

:找一条你设计的PCB走线,用仿真工具计算它的特性阻抗,对比你的设计目标。

测量验证

:如果你有示波器,测量一下高速信号的波形,看看是否存在反射、过冲等问题。

深入学习

:高速设计领域还有很多进阶主题,如电源完整性、EMC设计、差分信号高级技巧等,可以逐步深入。

记住:理论是基础,但实践是检验真理的唯一标准。多动手、多验证、多总结,你会在高速设计的道路上越走越远。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)