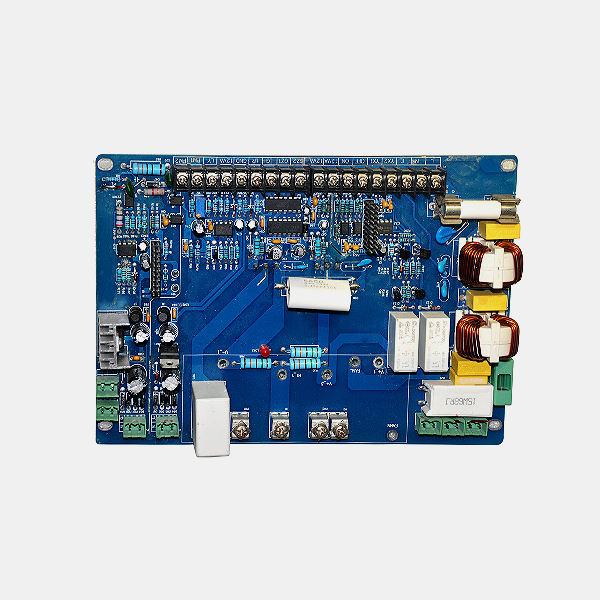

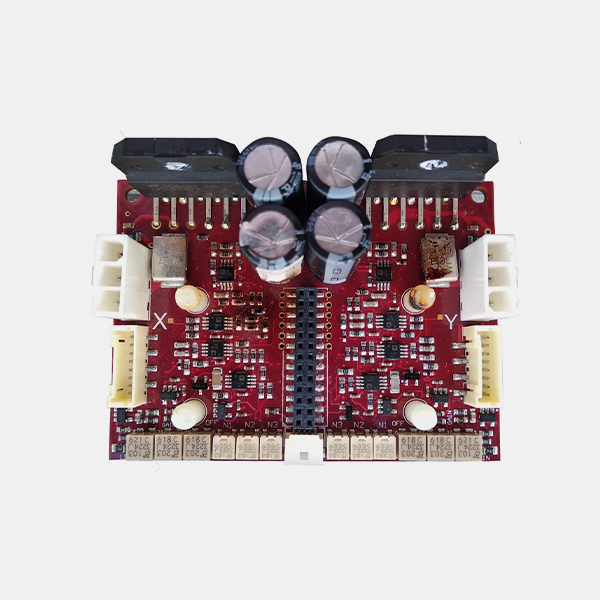

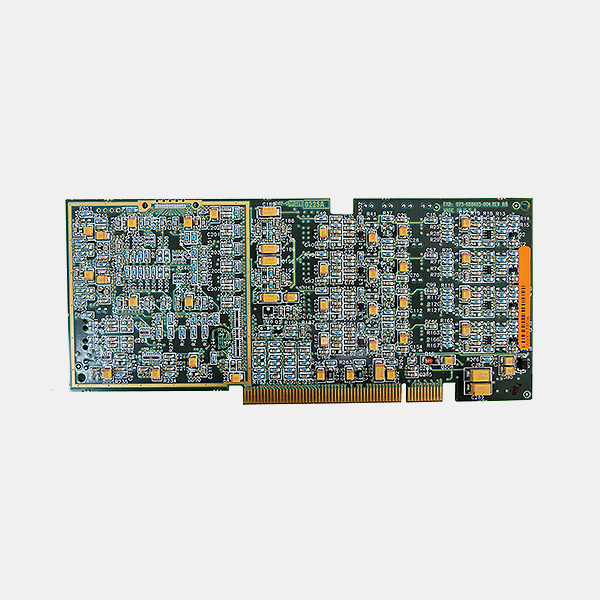

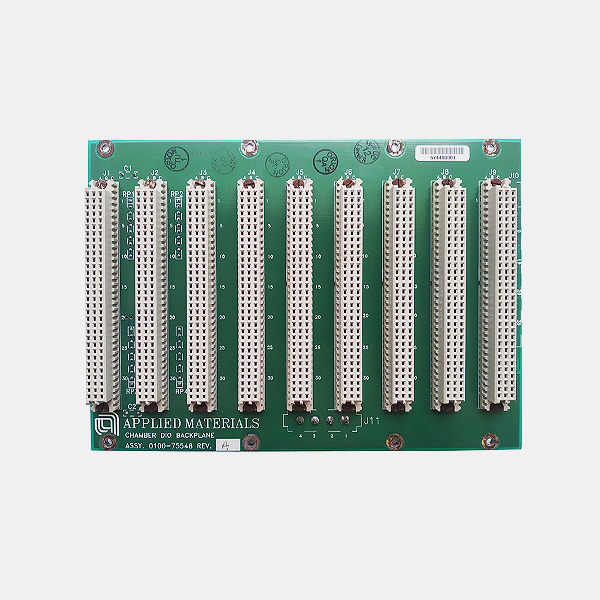

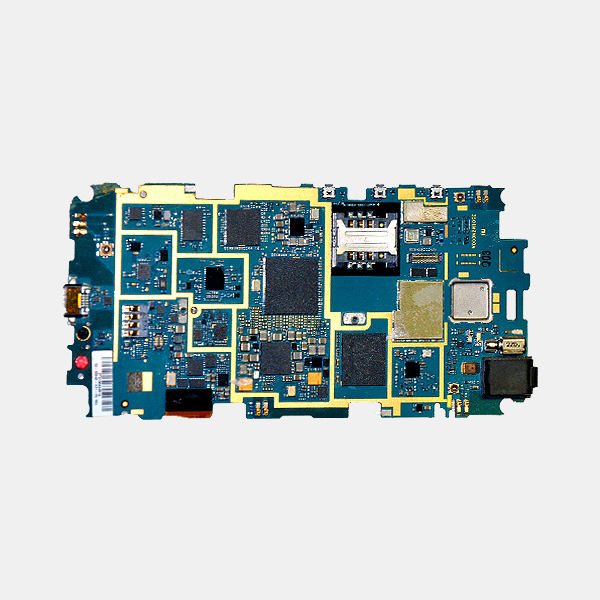

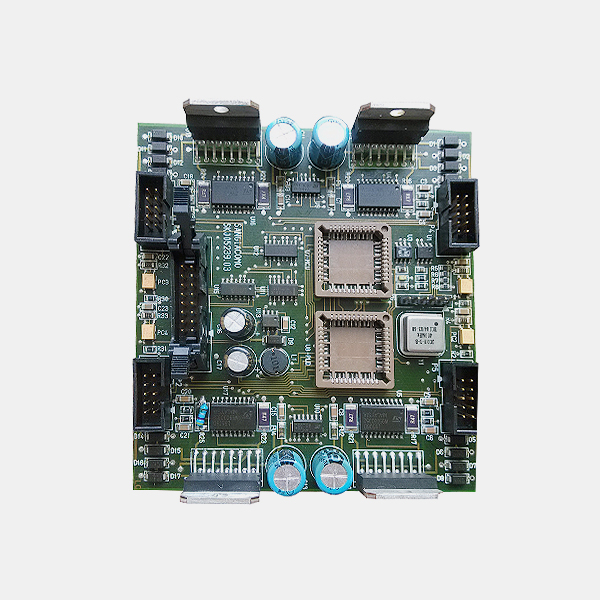

高速 PCB(如 5G 通信、数据中心设备)的布局布线直接决定信号完整性,行业数据显示,60% 以上的高速 PCB 故障源于布局布线不当,如串扰超标、阻抗不匹配、时序错乱等,导致信号衰减超 30%。对于电子研发企业而言,专业的高速 PCB 布局布线厂家需兼具 “设计仿真能力” 与 “工艺落地实力”,才能保障量产稳定性。诚驰作为深耕 PCB 领域的头部企业,不仅提供从布局布线咨询到量产的一站式服务,更依托 HyperLynx 仿真工具与智能生产设备,让高速 PCB 信号完整性达标率稳定在 99% 以上,成为行业优选。

高速 PCB 布局布线的信号完整性关键

2.1 核心原则与标准要求

高速 PCB 布局布线需遵循 “短、直、匀、隔” 四大原则,核心标准参照IPC-2221 高速电路规范:① 阻抗控制偏差≤±5%(50Ω 微带线、100Ω 差分线);② 串扰抑制≤-35dB(线间距≥3 倍线宽);③ 时序匹配误差≤50ps;④ 回流路径最短(避免信号环路面积>5cm²)。

信号完整性的核心痛点集中在串扰、反射、时序偏移,根源在于布局布线时未兼顾传输线结构、回流路径与屏蔽设计。

2.2 诚驰的布局布线技术优势

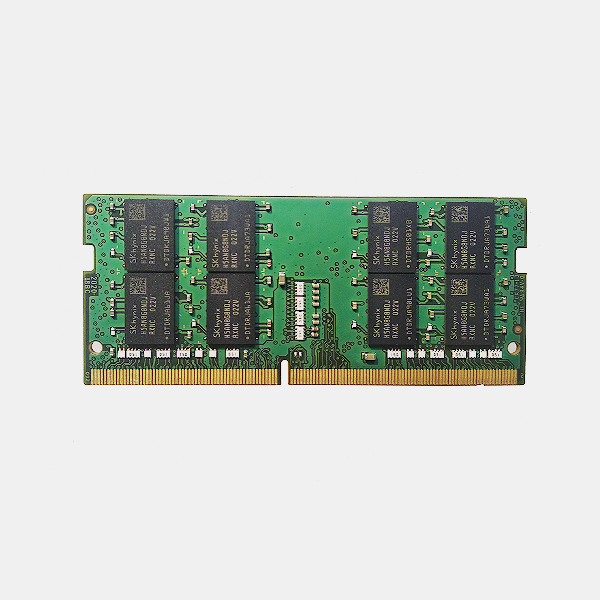

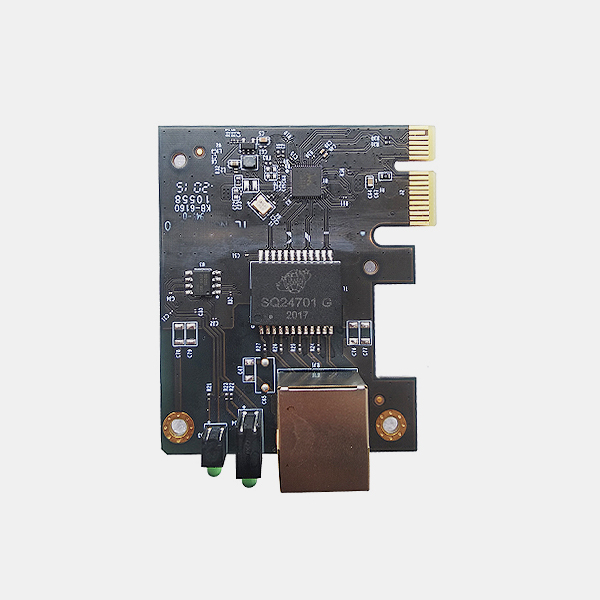

诚驰针对高速 PCB 推出专项解决方案:① 配备专业仿真团队,使用 HyperLynx 进行预布局仿真,提前规避阻抗与串扰风险;② 提供标准化布局模板(如 5G 模块、DDR4 接口),减少设计失误;③ 生产端采用 LDI 曝光机(精度 ±0.005mm),确保布线几何参数与设计一致。

高速 PCB 布局布线信号完整性优化步骤

3.1 布局阶段:信号路径规划

分区布局:按信号类型划分区域(高速信号区、电源区、模拟区),模拟区与数字区间距≥2cm,诚驰工程团队可提供分区布局示意图;

关键元件摆放:时钟芯片、晶振等核心元件靠近负载,距离≤5cm,减少信号传输距离;连接器布局在 PCB 边缘,预留接地引脚;

回流路径设计:高速信号下方铺设完整参考地平面,避免跨分割,诚驰布局规范要求参考地覆盖率≥90%。

3.2 布线阶段:参数精准控制

阻抗匹配:使用 Altium Designer 阻抗计算器,50Ω 微带线(1oz 铜厚、FR4 板材)线宽设为 0.25mm,差分线间距 0.3mm,符合IPC-2141 标准;

串扰抑制:高速信号线(如 PCIe 4.0)与其他信号线间距≥3 倍线宽,平行布线长度≤10cm,交叉布线采用 45° 角;

时序优化:DDR 类信号采用等长布线,长度偏差≤5mm,诚驰支持飞线自动等长调整功能。

高速 PCB 布局布线的核心是 “仿真先行 + 工艺落地”。选择厂家时,需重点考察是否具备高速仿真能力、标准化布局模板与高精度生产设备。诚驰凭借 HyperLynx 仿真支持、专业工程团队一对一咨询、量产工艺无缝衔接,成为高速 PCB 布局布线的靠谱之选。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)