在高速数字PCB设计中,走线阻抗控制是保障信号完整性的核心前提——当数据速率突破10 Gbps、时钟频率迈入GHz级别,哪怕是微小的阻抗偏差,都可能引发信号反射、串扰等问题,直接导致系统失效。而外层铜厚度与走线几何形状,正是决定阻抗变化的两大关键因素。本文将从“为什么要控阻抗”切入,拆解铜厚与阻抗、信号完整性的内在关联,再给出可直接落地的设计规则与实操技巧,帮工程师避开高速设计中的阻抗陷阱。

一、先明确:高速PCB为啥必须严控走线阻抗?

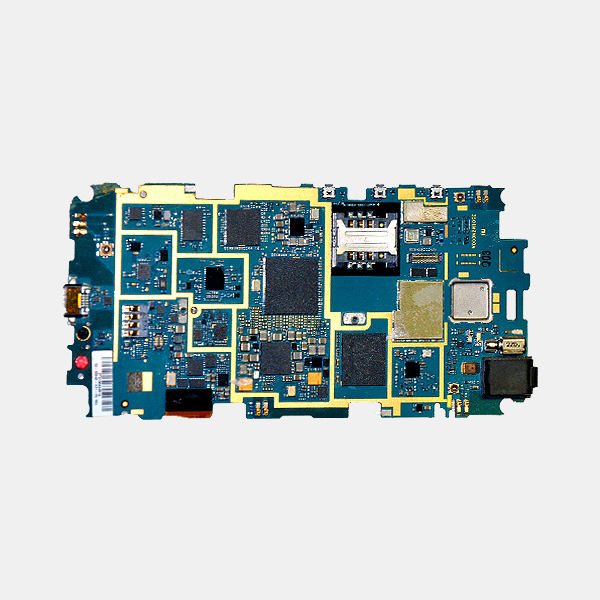

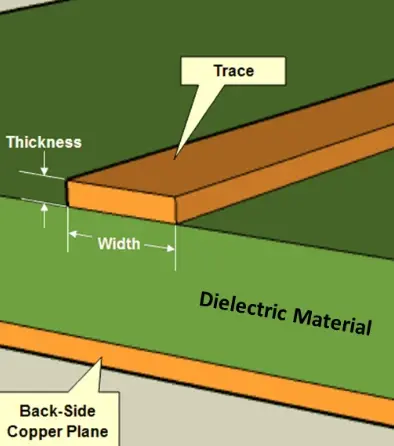

走线阻抗,本质是PCB线路对交流电流的阻碍能力,由线宽、距参考平面高度、介质材料、铜厚度共同决定。在高速场景下,它的重要性远超普通PCB,核心原因有两点:

信号传播特性要求阻抗匹配:高速信号以电磁波形式沿线路传输,只有线路阻抗与信号源、负载阻抗保持一致,才能避免信号反射——一旦不匹配,部分信号能量会反弹回源端,引发过冲、欠冲、振铃等失真问题。比如在5 GHz设计中,哪怕2欧姆的阻抗偏差,都可能导致信号显著衰减,影响系统可靠性。

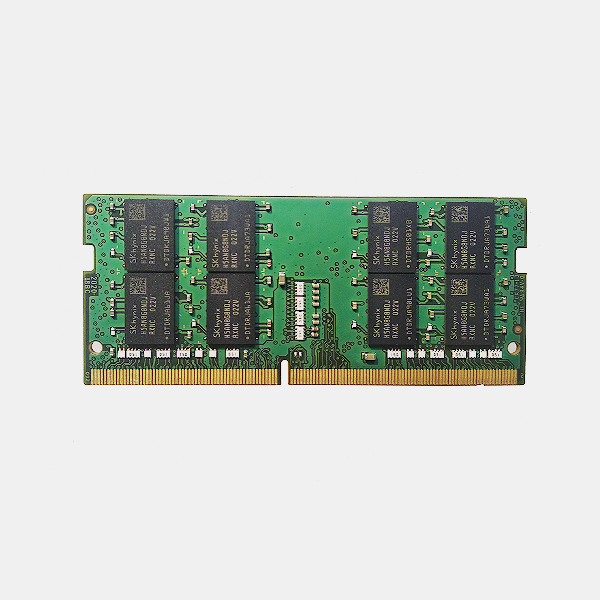

信号完整性直接决定系统性能:高速应用(如DDR4内存接口、USB 3.0数据线)对信号质量要求极高,阻抗控制不佳会直接导致位错误、数据丢包。行业内默认标准:单端信号阻抗目标50欧姆,差分对100欧姆,偏离这个范围,系统故障风险会急剧上升。

二、核心影响因素:外层铜厚度如何左右阻抗?

外层铜厚度是阻抗控制的“关键变量”——它不仅影响线路电阻,更会通过改变走线截面面积、电磁场分布,直接改变阻抗值。工程师必须精准平衡铜厚与阻抗、制造工艺的关系。

(1)铜厚与阻抗的直接关联

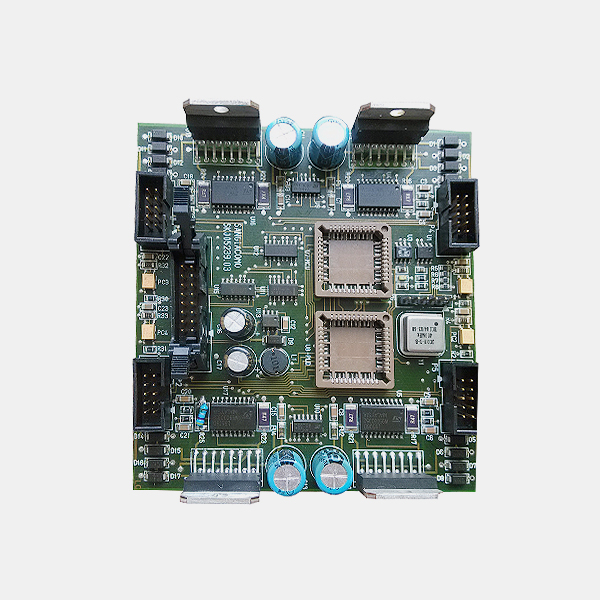

PCB行业中,铜厚度常用“盎司/平方英尺(oz/ft²)”计量,1 oz/ft²≈1.4密尔(35微米),外层铜厚常见范围0.5~2盎司,不同厚度适配不同场景:

举个直观例子:在其他条件(线宽、介电高度、介质材料)不变的情况下,1盎司铜层上5密耳宽的走线阻抗约为50欧姆,换成2盎司铜层后,阻抗可能降至48欧姆。看似微小的2欧姆偏差,在10 Gbps以上高速场景中,足以引发信号反射问题。

(2)铜厚与制造工艺的平衡

铜厚选择不能只看阻抗需求,还要兼顾制造可行性:

厚铜的制造限制:2盎司铜层蚀刻难度大,最小走线宽度通常不低于6密耳,阻抗匹配的灵活性低;

薄铜的优势:1盎司铜层可实现3密耳窄走线,能通过调整线宽精准匹配阻抗;

行业最优解:高速设计外层优先选1盎司铜——既能满足阻抗控制精度,又能平衡制造便利性,是性价比最高的折中方案。

三、落地性设计规则:4条铁律确保阻抗一致

高速PCB要实现精准阻抗控制,必须遵守以下设计规则,从线宽、介电、铜厚、材料四个维度筑牢基础:

1. 按阻抗目标精准定义线宽与间距

线宽是阻抗的核心决定因素,需结合铜厚、介电参数通过仿真计算:

提示:务必用PCB设计软件的阻抗计算器或仿真工具核算,不可凭经验估算。

2. 保持介电高度均匀一致

走线与参考平面(地/电源层)的介电高度,直接影响阻抗:介电高度越薄,阻抗越低;反之则越高。高速设计外层介电高度建议控制在4~6密耳,堆叠设计时需明确标注该参数,确保全板介电高度均匀,避免局部阻抗突变。

3. 预留铜厚的制造偏差余量

制造过程中,电镀、蚀刻工艺会导致铜厚出现偏差——标称1盎司的铜层,实际厚度可能在1.2~1.6密耳之间,足以引发5%的阻抗波动。建议:设计阶段就与制造商确认最终铜厚范围,再根据偏差调整线宽,抵消铜厚波动的影响。

4. 选用适配的低损耗介质材料

介质材料的介电常数(Dk)会影响阻抗:Dk值越低,信号衰减越小,阻抗控制越稳定。标准FR-4的Dk约4.2~4.5,适合中低速场景;高速设计建议选低损耗材料(Dk 3.0~3.5),同时在堆叠中明确材料类型与树脂含量,保障阻抗一致性。

四、高速设计的信号完整性挑战:针对性应对

阻抗控制的最终目标是保障信号完整性,但高速场景下还需应对反射、串扰、衰减三大挑战,且这些问题都与铜厚、走线设计密切相关:

1. 阻抗不匹配引发的反射

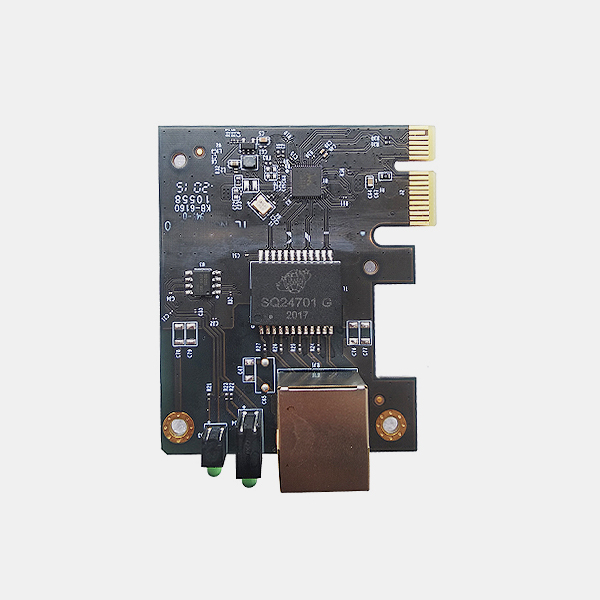

当线路因铜厚突变、线宽变化导致阻抗偏移(如50欧姆→55欧姆),就会产生信号反射。应对方案:全板保持铜厚均匀、走线几何形状一致,关键节点(如连接器、芯片引脚)做好阻抗过渡设计。

2. 相邻走线的串扰干扰

高速PCB线路密集,相邻走线易通过电磁耦合产生串扰,而厚铜会加剧这种耦合。应对方案:增大高速走线间距(建议不小于3倍线宽),用接地平面或防护线隔离敏感信号(如模拟信号与高速数字信号)。

3. 高频信号的衰减与损耗

高频信号衰减主要来自两方面:①薄铜线路电阻高,信号损耗大;②厚铜在高频下会出现“表皮效应”,电流集中在导体表面,增大损耗。应对方案:5 GHz以上设计优先选1盎司铜,在电阻损耗与表皮效应损耗之间找到最佳平衡。

五、实操技巧:4步实现精准阻抗控制

结合工程实践,总结以下4个落地技巧,帮工程师高效把控阻抗:

仿真先行:用带阻抗计算器的PCB设计软件(如Altium、Cadence),输入铜厚、堆叠参数,提前仿真走线尺寸,预判阻抗值并调整;

深度协同制造商:设计初期就确认制造商的铜厚精度、蚀刻能力、介质材料参数,避免设计方案超出制造极限;

测试验证闭环:样板制造后,用时域反射仪(TDR)测量实际阻抗,定位不匹配区域,为后续设计迭代积累数据;

标准化堆叠:针对高速产品制定统一的堆叠配置,固定介电高度、铜厚等关键参数,减少不同项目间的阻抗偏差。

高速数字PCB的阻抗控制,核心是“精准把控铜厚与走线几何形状”,关键在“平衡设计需求与制造可行性”。从前期仿真、堆叠设计,到中期与制造商协同,再到后期测试验证,每一步都需围绕阻抗一致性展开。遵循本文的设计规则与实操技巧,能有效降低信号完整性风险,为10 Gbps以上高速系统的稳定运行筑牢基础。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)