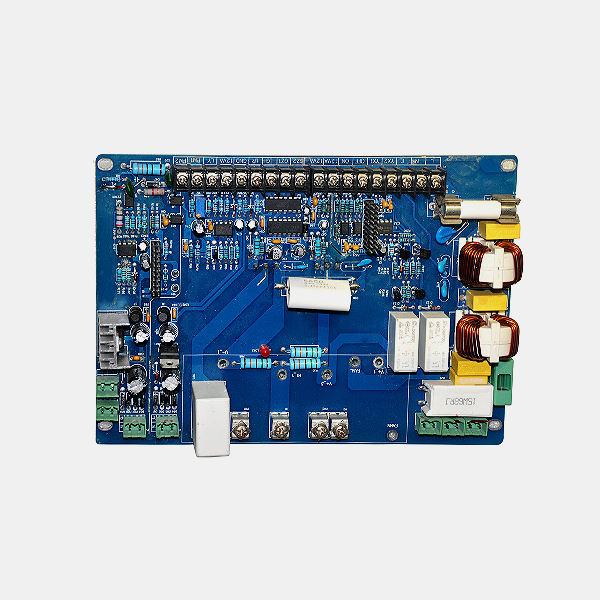

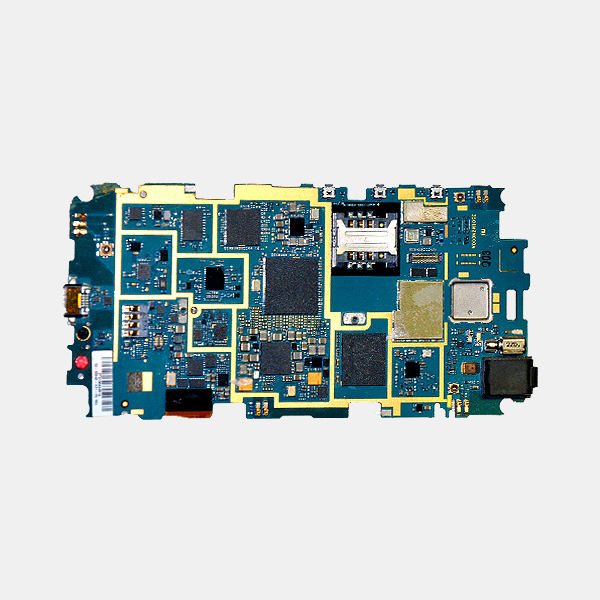

做过高密度八层PCB的工程师都懂,高速信号设计里,阻抗就是“生命线”,尤其是八层板承载着6G预研、高速通信、工业控制等高频高速信号,阻抗偏差一点点,信号就会失真、反射、丢包,这就是八层PCB设计里第二大核心陷阱——阻抗控制失控。

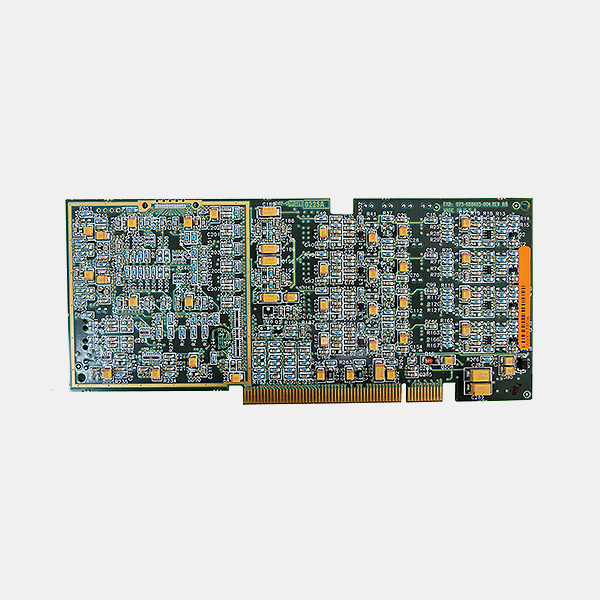

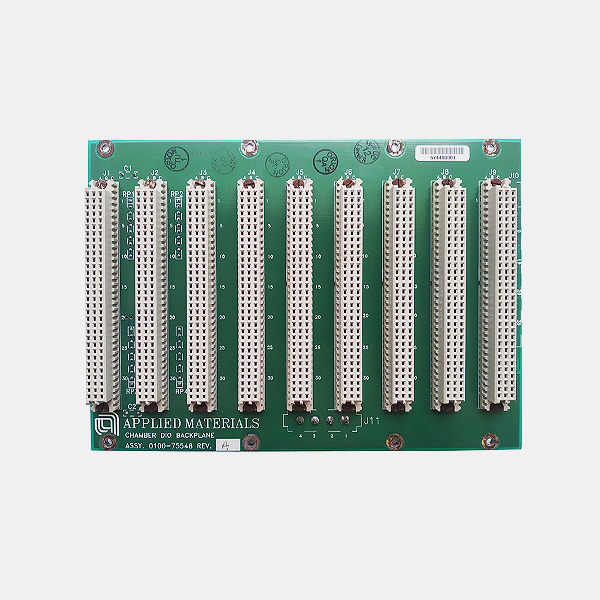

首先要明确:八层PCB的阻抗控制,和四层板完全不是一个难度,四层板信号层只有参考地平面单一,阻抗计算相对简单,而八层板有多层信号层,分别参考内层地、内层电源,还有差分对、共面阻抗等多种形式,再加上盲埋孔、线路拐角、过孔寄生参数的影响,阻抗控制难度直线上升。最常见的阻抗陷阱,就是只算理论值,不考虑实际工艺误差;差分对等长不达标,阻抗失衡;过孔、焊盘破坏阻抗连续性;叠构变更后不重新核算阻抗,每一个坑都能让高速信号直接“翻车”。

先讲最普遍的坑:理论阻抗和实际生产脱节,工程师闭门造车算参数。很多同行做设计时,直接用SI9000软件输个介电常数、介质厚度、线宽线距,算出理论阻抗就完事,完全忽略生产工艺的误差。比如八层板常用的高速环保基材,介电常数(Dk)会随着频率、温度波动,理论值和实际值有偏差;生产中层压后的介质厚度,会因为胶片流动、压力误差,和设计值差几微米,这些微小偏差,在6G高频信号下,会直接导致阻抗偏差超过±10%,远超行业要求的±5%公差。

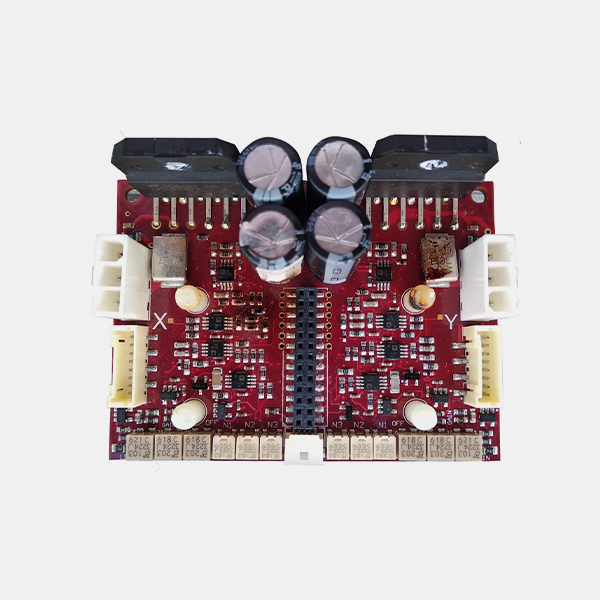

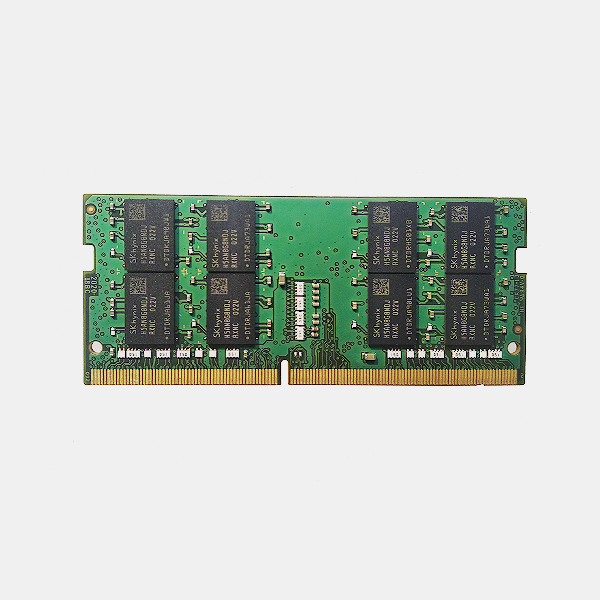

第二个致命陷阱:差分对不等长、不对称,阻抗失衡,相位误差超标。八层板里的高速差分信号(比如USB3.0、PCIe、射频差分信号),要求两根线等长、等距、同环境,阻抗严格一致,不然会出现差分转共模干扰,信号抖动变大,传输速率上不去。很多工程师布线时,为了赶进度,随便拉差分线,长短差超过5mil,或者旁边走了其他信号线干扰,导致两根线阻抗不一样,看似小问题,实则在高速传输下直接失效。

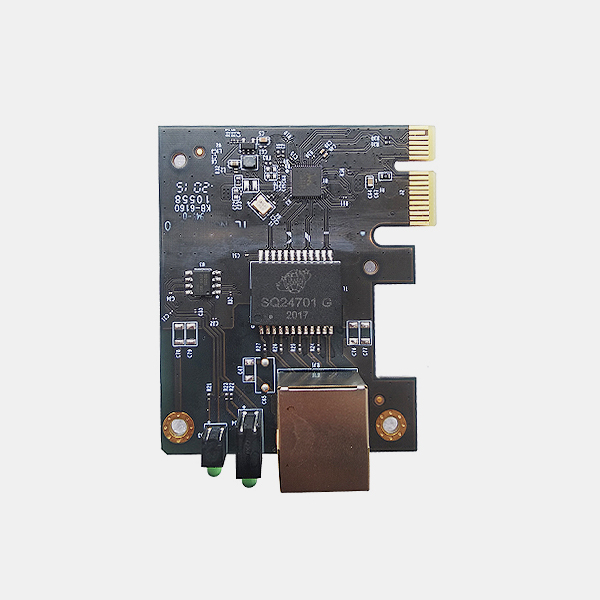

第三个隐形陷阱:过孔、焊盘、线路拐角破坏阻抗连续性,产生寄生参数。八层板高密度布线,难免要打过孔,尤其是盲埋孔,过孔的寄生电感和电容,会让局部阻抗突变,信号在这里产生反射;还有焊盘过大、线路走直角,都会改变局部阻抗,形成信号“瓶颈”。更麻烦的是,很多工程师为了修复阻抗,随意加匹配电阻,不仅增加元器件数量,还让布局更乱,既增加了功耗,又浪费材料,不符合6G低碳减排、高集成的要求。

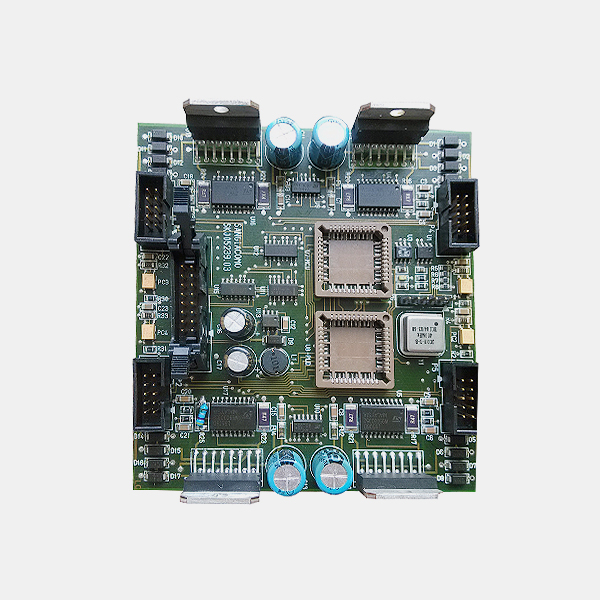

给大家整理了一套八层板阻抗避坑实战法则,适配6G高频需求:第一,叠构确定后,结合生产厂家的工艺能力,核算实际介质厚度、铜厚、基材实际Dk值,用仿真软件做多次阻抗仿真,预留工艺误差余量,公差严格控制在±5%以内,高频信号甚至要做到±3%;第二,差分对严格等长等距,长短差控制在2mil以内,远离干扰源,两侧加接地过孔隔离,既保证阻抗平衡,又让布线规整,贴合美学要求;第三,尽量减少过孔数量,高速信号避免换层,必须换层时用短过孔,就近加接地过孔,消除寄生参数;第四,叠构、基材、线宽任何一项变更,必须重新核算阻抗,杜绝“一劳永逸”。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)