对于硬件工程师而言,想要做好反射抑制,光懂理论远远不够,更要精准识别 PCB 设计中那些高频出现的、会导致阻抗突变的典型场景。这些场景往往隐藏在布局布线的细节中,稍有不慎就会成为信号反射的重灾区,最终引发严重的信号完整性问题。

第一个高频出现的反射源,是走线本身的物理结构不连续。很多工程师在布线时,为了绕开器件、过孔,会随意改变走线的线宽,这是最基础也最容易被忽略的错误。我们在第一篇中讲过,传输线的特征阻抗和线宽直接相关,线宽突然变大,会导致单位长度电容增大,特征阻抗降低;线宽突然变小,特征阻抗会升高,这种线宽突变会直接形成阻抗不连续节点,引发信号反射。行业内的通用设计规则是:同一组高速信号的走线,必须全程保持线宽一致,除非是为了阻抗补偿进行的精准微调,否则绝对禁止随意改变线宽。

除了线宽突变,走线拐角也是引发反射的常见场景。直角拐角是高速信号布线的大忌,其核心危害有两点:一是直角拐角的外侧线宽会自然变大,导致阻抗降低,形成阻抗突变;二是直角拐角的拐点处会产生额外的寄生电容,进一步加剧阻抗不连续,同时还会延长信号的上升沿时间。对于速率超过 1Gbps 的高速信号,必须禁止使用直角拐角,优先采用 45 度斜角拐角,对于超高速信号(如 10Gbps 以上),推荐采用圆弧拐角,且圆弧半径需大于走线线宽的 3 倍,最大限度降低拐角带来的阻抗波动。

第二个重灾区,是 PCB 过孔带来的阻抗不连续。在多层 PCB 设计中,过孔是实现层间互连的必备结构,但对于高速信号而言,过孔是链路中最主要的反射源之一。过孔之所以会引发反射,核心是其存在固有的寄生电容和寄生电感,导致过孔的阻抗和传输线的特征阻抗出现明显偏差。过孔的寄生电容主要来自焊盘和反焊盘之间的耦合,会导致过孔阻抗降低;寄生电感主要来自过孔的孔壁金属,会导致阻抗升高,两者共同作用下,过孔的阻抗往往会和目标阻抗出现 10%-30% 的偏差,直接引发强烈的信号反射。

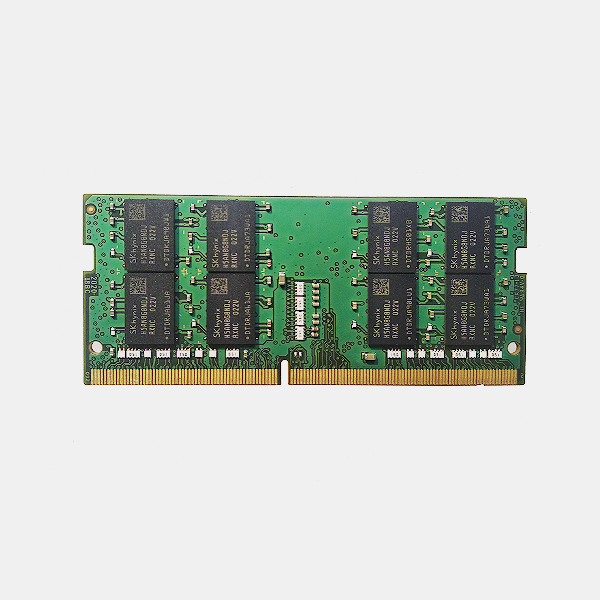

更需要警惕的是过孔的残桩(Stub)带来的反射问题。举个例子,在 8 层 PCB 中,信号从顶层(第 1 层)通过通孔传输到第 3 层,那么第 3 层到底层(第 8 层)的这段过孔,就是没有任何电气连接的残桩。这段残桩相当于在传输线上并联了一个开路的传输线,当残桩长度超过信号上升沿对应有效波长的 1/20 时,会产生严重的谐振效应,引发极强的反射,直接导致信号波形畸变。对于 DDR5、PCIe 4.0 及以上的超高速信号,过孔残桩的影响是致命的,必须通过背钻工艺将无用的残桩去除,将残桩长度控制在 8mil 以内,才能有效抑制反射。

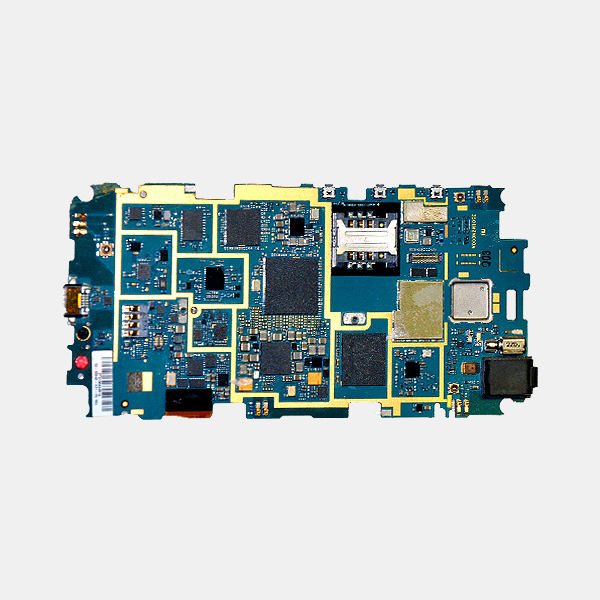

第三个容易被忽略的反射源,是器件封装、连接器与互连结构的寄生参数。芯片的封装内部,焊盘、键合线、引脚都会存在寄生电感和寄生电容,这些寄生参数会导致芯片输入输出端的阻抗和传输线阻抗不匹配,形成反射节点。很多工程师在做仿真时,只关注 PCB 走线的阻抗,却忽略了芯片封装的寄生参数,最终导致仿真结果和实际测试结果出现巨大偏差。

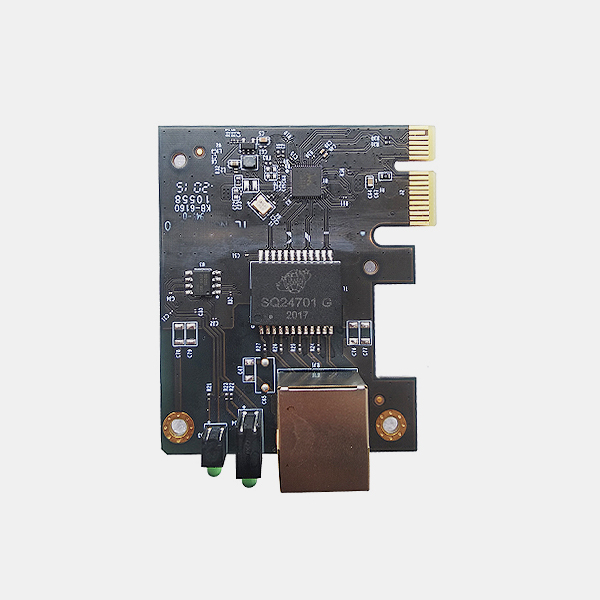

连接器、接插件、金手指等板间互连结构,也是高速链路中的关键反射点。这些结构的物理尺寸、引脚间距、接触方式都会导致阻抗突变,尤其是普通的排针排母,其寄生电感极大,在速率超过 500Mbps 的信号中就会产生明显的反射。对于高速板间互连,必须选用阻抗可控的专用高速连接器,同时在设计时优化连接器焊盘的出线方式,做阻抗补偿,最大限度降低阻抗波动。此外,很多工程师为了测试方便,在高速走线上额外添加测试焊盘,这些焊盘会导致走线阻抗突变,形成反射源,正确的做法是采用无残桩的测试点设计,直接在走线上设置测试点,禁止通过分支走线引出测试焊盘。

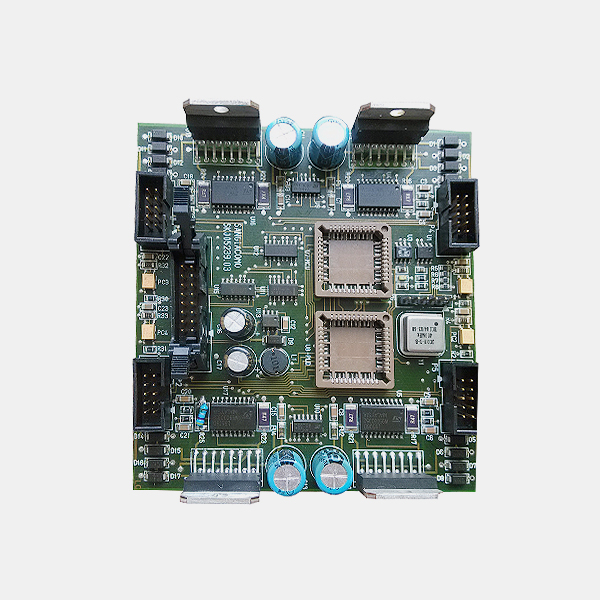

第四个核心反射源,是参考平面断裂与回流路径不完整。传输线的特征阻抗,是由走线和其相邻的参考平面共同决定的,高速信号的回流电流,会沿着参考平面中与走线对应的路径流动,这是保证阻抗连续的核心。当高速走线跨过电源平面和地平面之间的缝隙,也就是我们常说的 “跨分割” 时,信号的回流路径会被强行打断,回流电流只能绕路流动,导致回流路径变长,回路电感急剧增大,传输线的特征阻抗出现突变,引发强烈的信号反射,同时还会带来严重的 EMI 问题。

PCB 设计中的信号反射,绝大多数都来自于这些细节场景的阻抗不连续。很多时候,工程师花了大量精力做端接匹配,却因为一个过孔残桩、一处走线跨分割、一个直角拐角,导致反射抑制效果大打折扣。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)