负载电容作为 PCB 设计的隐形核心,其问题往往隐蔽、复杂、影响深远 —— 轻则性能下降,重则系统失效。

一、负载电容的十大典型设计问题

1. 晶振不起振 / 频率偏移(最常见)

问题:晶振无输出、输出幅度低、频率偏差大(>±50ppm)

原因:负载电容严重不匹配(偏小→频率偏高;偏大→频率偏低);未计入 PCB 寄生电容。

案例:标称 Cₗ=16pF,外接 C₁=C₂=16pF,未计 8pF 寄生,实际 Cₗ=16pF,偏小→频率偏高 80ppm。

2. 高速总线时序违规 / 死机

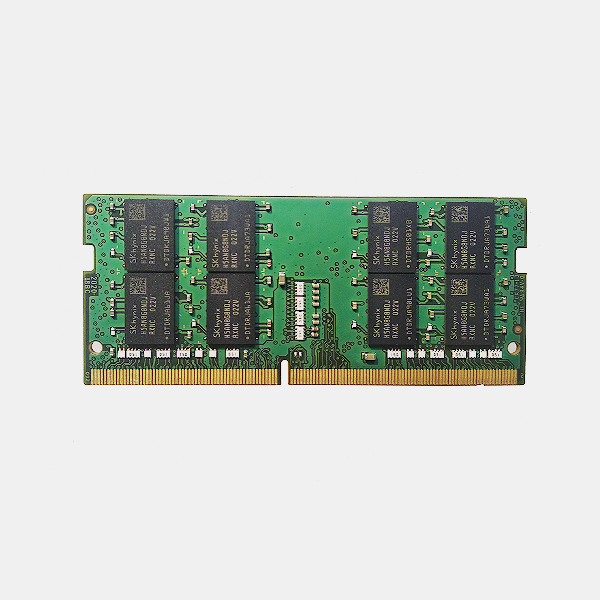

问题:DDR/PCIe 通信失败、数据错误、系统死机

原因:总负载电容超标(>12pF);同组线负载差异大(>1pF)→ 时序偏差超阈值。

3. 信号边沿钝化 / 眼图差

问题:信号上升沿 > 1ns、眼图闭合、误码率高

原因:走线过长、过孔过多、参考平面不完整→分布电容过大。

4. 时钟抖动大 / 相位噪声差

问题:时钟抖动 > 100ps、射频相位误差超标

原因:负载电容波动(温漂、材质差);寄生电容不稳定→谐振频率漂移。

5. 功耗异常偏高 / 发热严重

问题:动态功耗超设计值 20%+、芯片局部发热

原因:总负载电容过大→充放电电流激增(P∝Cₗ)。

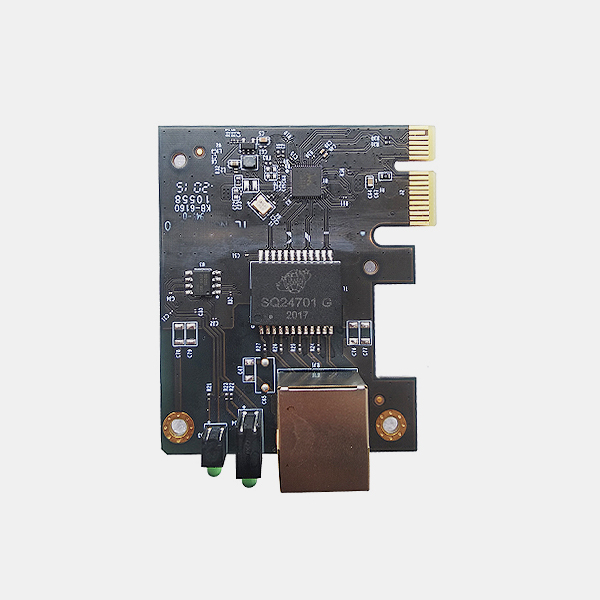

6. 射频信号反射 / 增益低

问题:射频驻波比 > 1.5、传输损耗 > 5%、通信距离短

原因:匹配负载电容错误,未计入过孔 / 焊盘寄生→阻抗失配。

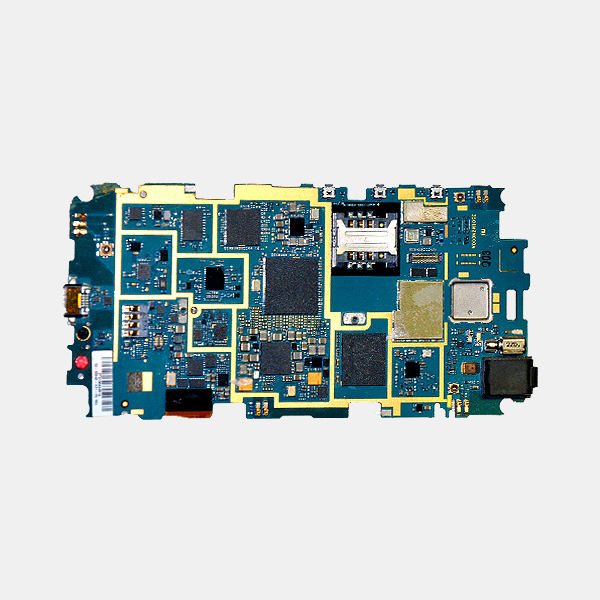

7. 低速通信误码(SPI/I²C)

问题:高速模式下(>10MHz)通信失败、数据丢包

原因:总线负载电容 > 20pF→边沿过缓,建立时间不足。

8. 温漂导致性能漂移

问题:低温 / 高温下频率偏移、信号质量下降

原因:匹配电容用 X7R(温漂 ±15%)→ 负载电容随温度大幅变化。

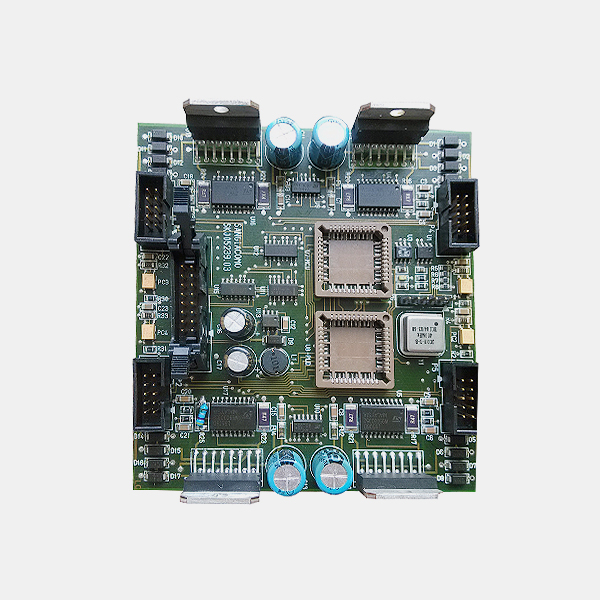

9. 量产一致性差

问题:部分板卡功能正常、部分异常,良率 < 90%

原因:PCB 板材 / 介质厚度公差大、寄生电容波动→负载电容不一致。

10. EMC/EMI 超标

问题:辐射干扰超标、抗干扰能力差

原因:负载电容与走线电感谐振→产生高频辐射噪声。

二、负载电容故障的诊断流程(四步法)

当出现上述问题时,按以下流程精准定位负载电容故障:

步骤 1:参数核对 —— 基础检查

核对晶振标称 Cₗ、芯片 Cᵢₙ、板材 Dk、介质厚度等核心参数。

检查外接电容值、材质、精度是否正确(如晶振是否用 NPO)。

步骤 2:理论计算 —— 误差分析

重新计算总负载电容,计入所有寄生(Cᵢₙ+Cₚₙₙ+Cₛₜᵣₐᵧ)。

对比设计值与实际计算值,判断偏差方向(偏大 / 偏小)。

步骤 3:实物测量 —— 精准验证

工具:LCR 数字电桥(1MHz 测试频率)、阻抗分析仪。

测试方法:

晶振电路:断电后测 OSC 引脚对地电容 → 即为实际 Cₗ。

高速电路:用 TDR(时域反射仪)测传输线负载电容。

判定:实测值与标称值偏差 >±5% → 负载电容故障。

步骤 4:定位寄生源 —— 优化整改

用 3D 仿真分析走线、过孔、焊盘的寄生分布。

针对性整改:缩短走线、减少过孔、优化焊盘、更换低 Dk 板材。

三、量产调试与整改方法

1. 晶振电路量产校准

预留微调焊盘:贴装 0402 空盘,量产时根据实测频率,贴装 ±0.5pF~±2pF NPO 电容校准。

批量测试:每批次抽测 10 块板,确保负载电容偏差 <±3%。

2. 高速总线负载超标整改

方案 A:缩短走线(最有效)→ 移除冗余长度,控制 < 5cm。

方案 B:减少过孔 → 背钻现有过孔、删除冗余过孔。

方案 C:更换低 Cᵢₙ芯片 → 降低固有负载基数。

3. 温漂问题整改

全部更换为 NPO/COG 材质电容(温漂 ±30ppm)。

优化布局:晶振远离热源(CPU、电源),温度波动 <±5℃。

4. 量产一致性提升

锁定板材供应商与料号,控制 Dk 公差 ±2%、介质厚度 ±10%。

标准化布局布线:同类型产品采用统一模板,寄生电容波动 <±0.5pF。

四、先进技术下的负载电容发展趋势

随着 5G/6G、AI、Chiplet、柔性电子的发展,负载电容技术正朝着更小、更稳、更精、集成化方向演进:

1. 超低寄生封装与基板技术

芯片级:2.5D/3D 封装、Chiplet → 缩短互联距离,芯片输入电容降至0.1~0.5pF。

PCB 级:超薄基板(<0.3mm)、埋容技术 → 分布电容降低 40%,负载一致性提升。

2. 自适应负载匹配技术

芯片内置可编程负载电容阵列(1~16pF,步长 0.1pF)→ 量产时自动校准,无需外接电容。

自适应电路:实时检测频率 / 信号质量,动态调整负载电容,适应温度、电压变化。

3. 新材料突破

超低 Dk 材料(Dk=2.2~3.0)→ 分布电容降低 30%~50%,适配 6G 毫米波(110GHz+)。

高稳定介质:温漂 <±1ppm 的特种板材→负载电容温度稳定性提升 10 倍。

4. 设计智能化

AI 驱动 EDA 工具:自动优化布局布线,实时计算负载电容,给出最优匹配方案。

数字孪生仿真:全流程虚拟验证负载电容,提前消除问题,研发周期缩短 50%。

5. 集成化负载解决方案

晶振 + 匹配电容集成封装(如 SMD 晶振内置 NPO 电容)→ 消除 PCB 寄生,匹配精度达 ±1%。

高速芯片内置终端匹配 + 负载校准→ 无需外部优化,即插即用。

随着电子技术向更高速度、更高频率、更高集成度发展,负载电容的重要性只会愈发凸显 ——掌控负载电容,就是掌控 PCB 性能的核心命脉。

欢迎来到深圳市诚驰电路科技有限公司官网!

欢迎来到深圳市诚驰电路科技有限公司官网! 关注微信

关注微信 网站地图

网站地图 English

English

廖工:18129931046

廖工:18129931046

扫码添加微信(林经理)

扫码添加微信(林经理)

扫码添加微信(廖 工)

扫码添加微信(廖 工)